Signals on the interface to the external plls, Signals on the interface to the external plls -15 – Altera Hybrid Memory Cube Controller User Manual

Page 52

Signals on the Interface to the External PLLs

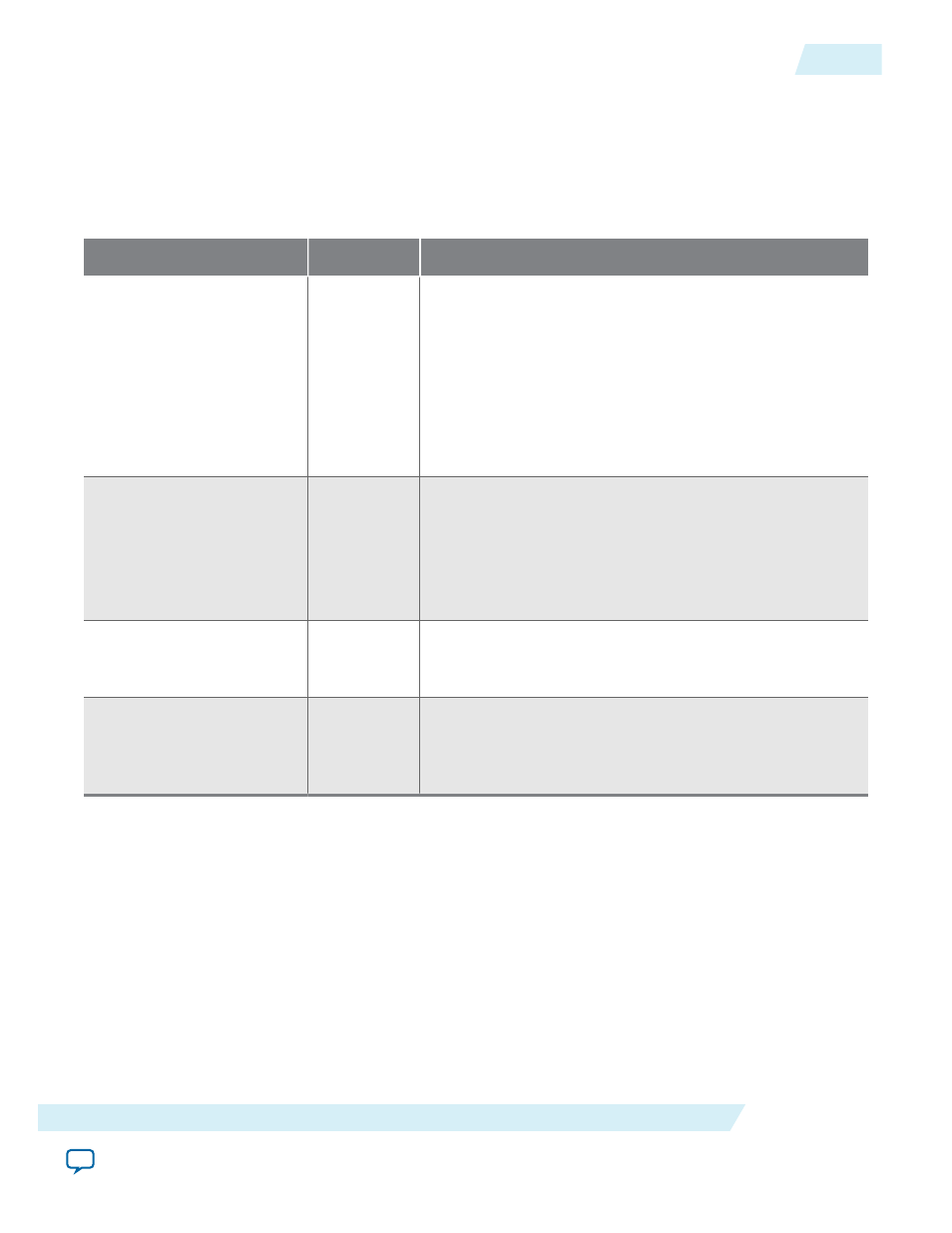

Table 4-9: HMC Controller IP Core External PLL Interface Signals

The HMC Controller IP core requires that you generate and connect a TX PLL IP core to each HMC Controller IP

core lane that connects to the HMC device. The HMC Controller IP core external PLL interface connects to these

PLL IP core instances.

Signal Name

Direction

Description

tx_bonding_

clocks[95:0]

(for full-

width IP cores)

tx_bonding_

clocks[47:0]

(for half-

width IP cores)

Input

Clocks for the individual transceiver channels. The input

clock to each transceiver channel has six bits.

You must connect this input bus to a set of external

transceiver TX PLL IP cores. You must parameterize each

external TX PLL IP core to specify an output frequency that

is 1/2 the per-lane data rate. For a 10 Gbps HMC Controller

IP core lane rate, the TX PLL IP core output frequency must

be 5 GHz; for a 12.5 Gbps lane rate, the TX PLL IP core

output frequency must be 6.25 GHz.

pll_locked

Input

PLL-locked indication from the external TX PLLs. User

logic must drive this input signal with the AND of the pll_

locked indications from the individual transceiver channels.

core_clk

can stabilize only after

pll_locked

is asserted.

The IP core deasserts the

core_rst_n

signal to indicate that

core_clk

has stabilized.

pll_powerdown

Output

Output signal from the IP core internal reset controller. The

IP core asserts this signal to tell the external PLLs to power

down.

pll_cal_busy

Input

PLL-busy indication from the external TX PLLs. When

multiple TX PLLs are instantiated, user logic must drive this

input signal with the OR of the pll_cal_busy indications

from the individual transceiver channels.

Related Information

on page 2-11

Describes how to generate and connect the external transceiver PLL IP cores to your HMC Controller IP

core.

Information about the Arria 10 transceiver PLLs and clock network.

UG-01152

2015.05.04

Signals on the Interface to the External PLLs

4-15

HMC Controller IP Core Signals

Altera Corporation