Transceiver reconfiguration signals, Transceiver reconfiguration signals -13 – Altera Hybrid Memory Cube Controller User Manual

Page 50

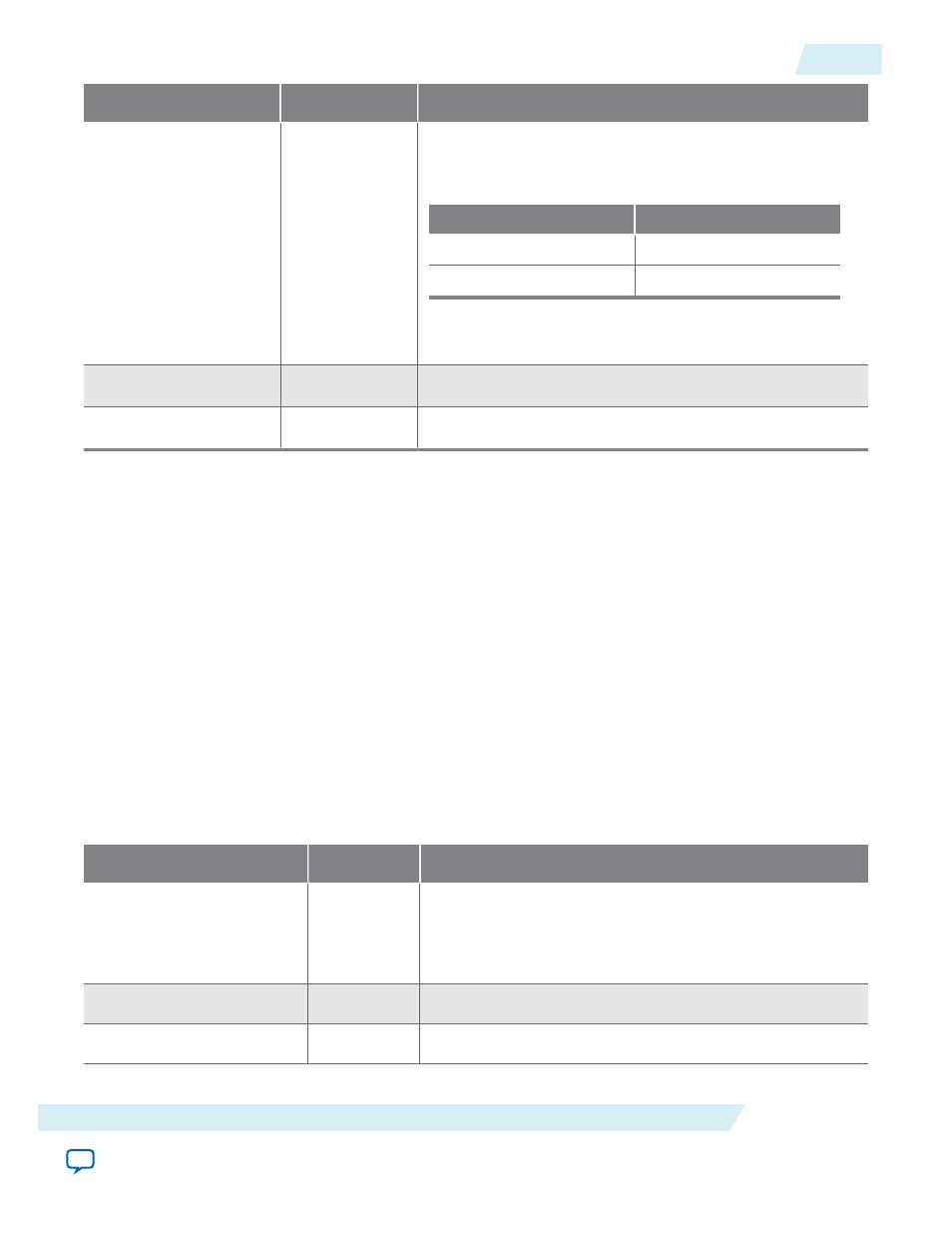

Clock Name

Direction

Description

core_clk

Output

Master clock for the HMC Controller IP core. The

transceiver generates

core_clk

. The frequency of

core_clk

is the lane rate divided by 32.

Lane Rate

core_clk

Frequency

10 Gbps

312.5 MHz

12.5 Gbps

390.625 MHz

core_clk

clocks the HMC Controller IP core signals,

including the signals on the control and status interface.

reconfig_clk

Input

Clock for the transceiver reconfiguration interface.

reconfig_reset

Input

Reset signal for the transceiver reconfiguration interface.

Related Information

•

Information about the Arria 10 dynamic reconfiguration interface clock and reset signals. The HMC

Controller IP core

reconfig_clk

and

reconfig_reset

input signals pass directly to the Arria 10

Native PHY IP core included in the HMC Controller IP core.

Transceiver Reconfiguration Signals

Altera provides a dedicated Avalon-MM interface, called the transceiver reconfiguration interface, to

access the transceiver registers. You access the transceiver registers through this dedicated interface and

not through the IP core general purpose control and status interface.

The Avalon-MM interface implements a standard memory-mapped protocol. You can connect an Avalon

master to this bus to access the registers of the embedded Arria 10 Native PHY IP core.

Table 4-8: HMC Controller IP Core Arria 10 Transceiver Reconfiguration Interface Signals

The

reconfig_clk

clocks the signals on the HMC Controller IP core Arria 10 transceiver reconfiguration

interface. The

reconfig_reset

input signal resets the interface.

Signal Name

Direction

Description

reconfig_address[13:0]

(full-width IP core)

reconfig_address[12:0]

(half-width IP core)

Input

Word address for reads and writes. This address has 14 bits

in full-width IP core variations and 13 bits in half-width IP

core variations.

reconfig_read

Input

You must assert this signal to request a read transfer.

reconfig_write

Input

You must assert this signal to request a write transfer.

UG-01152

2015.05.04

Transceiver Reconfiguration Signals

4-13

HMC Controller IP Core Signals

Altera Corporation