Initialization, Initialization -5 – Altera Hybrid Memory Cube Controller User Manual

Page 33

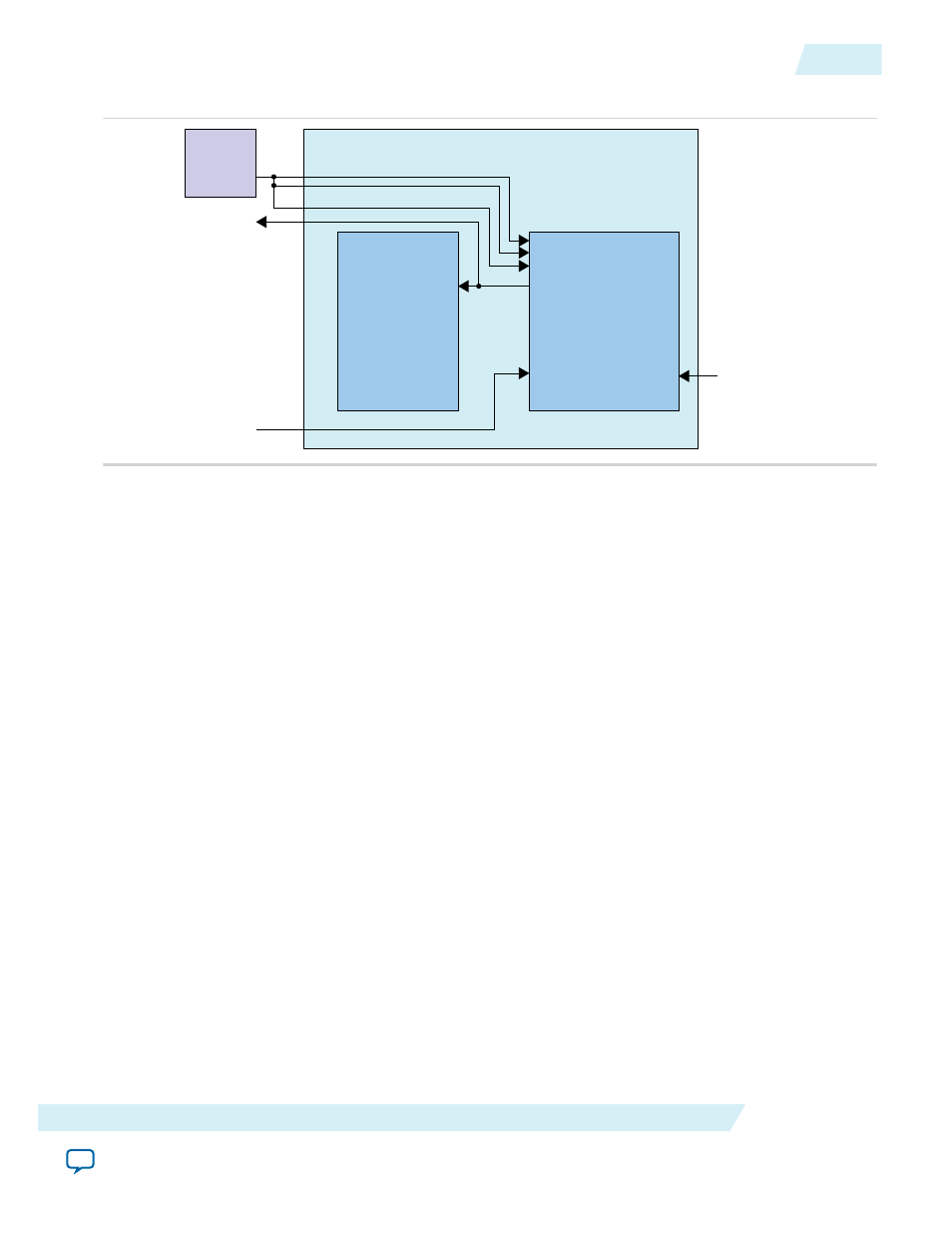

Figure 3-2: HMC Controller IP Core Clocking Diagram

TX PLL

pll_refclk0

HMC Controller IP Core

Transceiver

x16

core_clk

reconfig_clk

tx_bonding_clocks[95:90]

tx_bonding_clocks[5:0]

tx_clkout[CHANNELS-1:0]

reconfig_clk

[0]

rx_cdr_refclk0

...

Related Information

Lists the clock and reset signals and the relationships between them.

Initialization

When you assert the active low

rst_n

signal, you trigger initialization of the HMC Controller IP core, the

HMC device, and the HMC link that connects them. To ensure the correct sequence, you must connect

the HMC Controller IP core, the I

2

C master module, and the HMC device correctly.

The following signals control HMC Controller IP core, HMC link, and HMC device initialization:

•

rst_n

: Active low HMC Controller IP core input signal that triggers IP core initialization

•

hmc_p_rst_n

: HMC Controller IP core output signal. You should connect this signal to the active low

HMC device

P_RST_N

input signal.

P_RST_N

triggers HMC device initialization.

•

i2c_load_registers

: HMC Controller IP core output signal. You should connect this signal to the

I

2

C master module input signal that tells the I

2

C master module to load the configuration registers of

the HMC device.

•

i2c_registers_loaded

: HMC Controller IP core input signal that indicates the I

2

C master module

has completed its part in the initialization of the HMC device. You should connect this signal to the

I

2

C master module output signal that indicates successful completion of the HMC configuration

register load sequence.

The IP core reports link initialization status in the

InitializationState

field of the

LINK_STATUS

register at offset 0x10. The HMC device reports its own link iniitialization status in its own link interface

status registers.

UG-01152

2015.05.04

Initialization

3-5

Functional Description

Altera Corporation