M20k ecc support, M20k ecc support -6, At offset 0x38 and – Altera Hybrid Memory Cube Controller User Manual

Page 34: At offset 0x3c

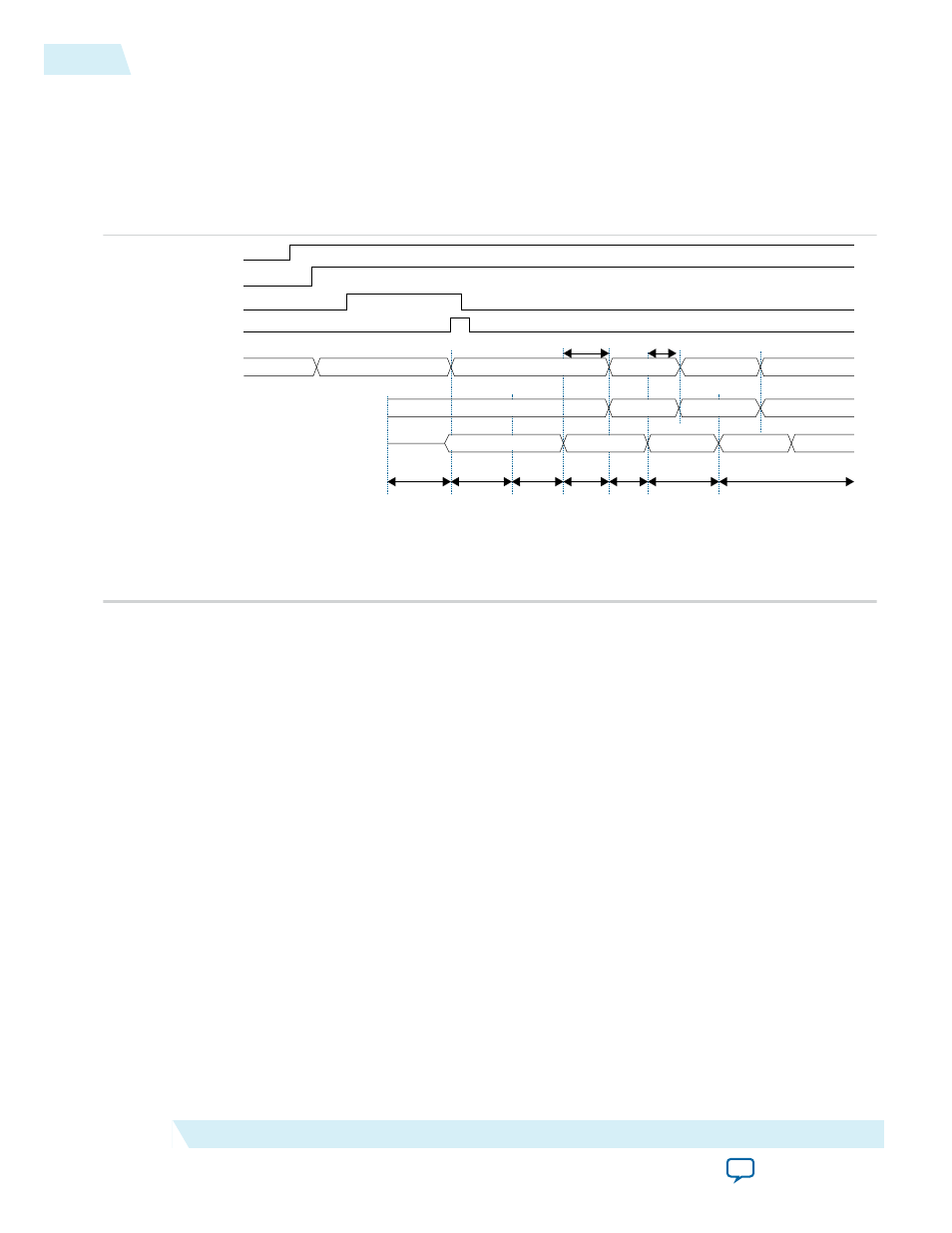

When you initialize the HMC link, recall the following HMC Controller IP core requirements:

• The HMC Controller IP core operates in Response Open Loop Mode, and you must configure the

HMC device to communicate correctly with the IP core in this mode.

• The IP core does not support the

TGA

field, so you must configure the HMC device to acknowledge

every non-posted Write request with a Write response packet.

Figure 3-3: HMC Link Initialization Sequence

rst_n

hmc_p_rst_n

(connects to HMC P_RST_N)

i2c_load_registers

i2c_registers_loaded

HMC Controller Status Register

(InitializationState field of

LINK_STATUS register)

Reset

Start HMC

Transmit Null

Transmit TSI

Wait for TRET

Active

Scrambled Null

TS1

Scrambled Null

Normal Traffic

Scrambled Null

TS1

Scr. Null & TRET

Normal Traffic

PRBS

HMC Controller IP Core TX HMC Link

(sending to HMC device)

HMC Controller IP Core RX HMC Link

(receiving from HMC device)

in Host Link Mode

High Z

0x01

Reset State

0x02

RX Clock Align

0x04

Descrambler

Sync

0x08

Non-Zero

Wait

0x10 & 0x20

TS1 Sync

& RX Lane

Deskew

0x40

Zero Wait

0x80

Active

HMC Device Link Interface Status

0x240002 - Link 0

0x250002 - Link 1

0x260002 - Link 2

0x270002 - Link 3

Notes:

1. HMC Controller IP core acquires descrambler sync. The Descrambler Sync field of the Lane Status register goes to all ones.

2. HMC Controller IP core does word and lane alignment. The Lanes Aligned bit pf the Link Status register goes to 1 and the Word Lock field of the Lane Status register goes to all ones.

(1)

(2)

PRBS

Related Information

•

Adding the External I2C Master Module

Describes the I

2

C master module requirements and the module's connections to the HMC Controller

IP core.

•

Signals on the Interface to the I2C Master

on page 4-9

Describes the detailed behavior of the I

2

C master module during initialization.

•

on page 4-8

This interface includes the

hmc_p_rst_n

signal.

•

•

on page 5-4

M20K ECC Support

If you turn on Enable M20K ECC support in your HMC Controller IP core variation, the IP core takes

advantage of the built-in device support for ECC checking in all M20K blocks configured in the IP core on

the device. The feature performs single-error correct, double-adjacent-error correct, and triple-adjacent-

error detect ECC functionality in the M20K memory blocks configured in your IP core.

The HMC Controller IP core reports ECC error statistics in the registers

RETRY_ECC_COUNT

at offset 0x38

and

RESPONSE_ECC_COUNT

at offset 0x3C.

3-6

M20K ECC Support

UG-01152

2015.05.04

Altera Corporation

Functional Description