Altera Hybrid Memory Cube Controller User Manual

Page 39

cycles. In half-width variations, the maximum payload size limits the interface to data bursts of 4 or fewer

core_clk

clock cycles. Write requests and read responses with a payload size that is not a multiple of the

bus size carry the end of the payload in the lower order bits of the data bus in the final clock cycle.

The application must provide the following routing and control information for every request it sends on

the TX data path interface:

• A well-formed HMC destination address.

• A unique 9-bit in-flight tag. This requirement does not apply to posted transaction requests. The

application can reuse a tag only after the previous transaction with that tag is completely resolved.

• A correct 3-bit cube ID.

In addition, the application must ensure that it sends a request only when it is able to receive the response

to the request as soon as that response arrives.

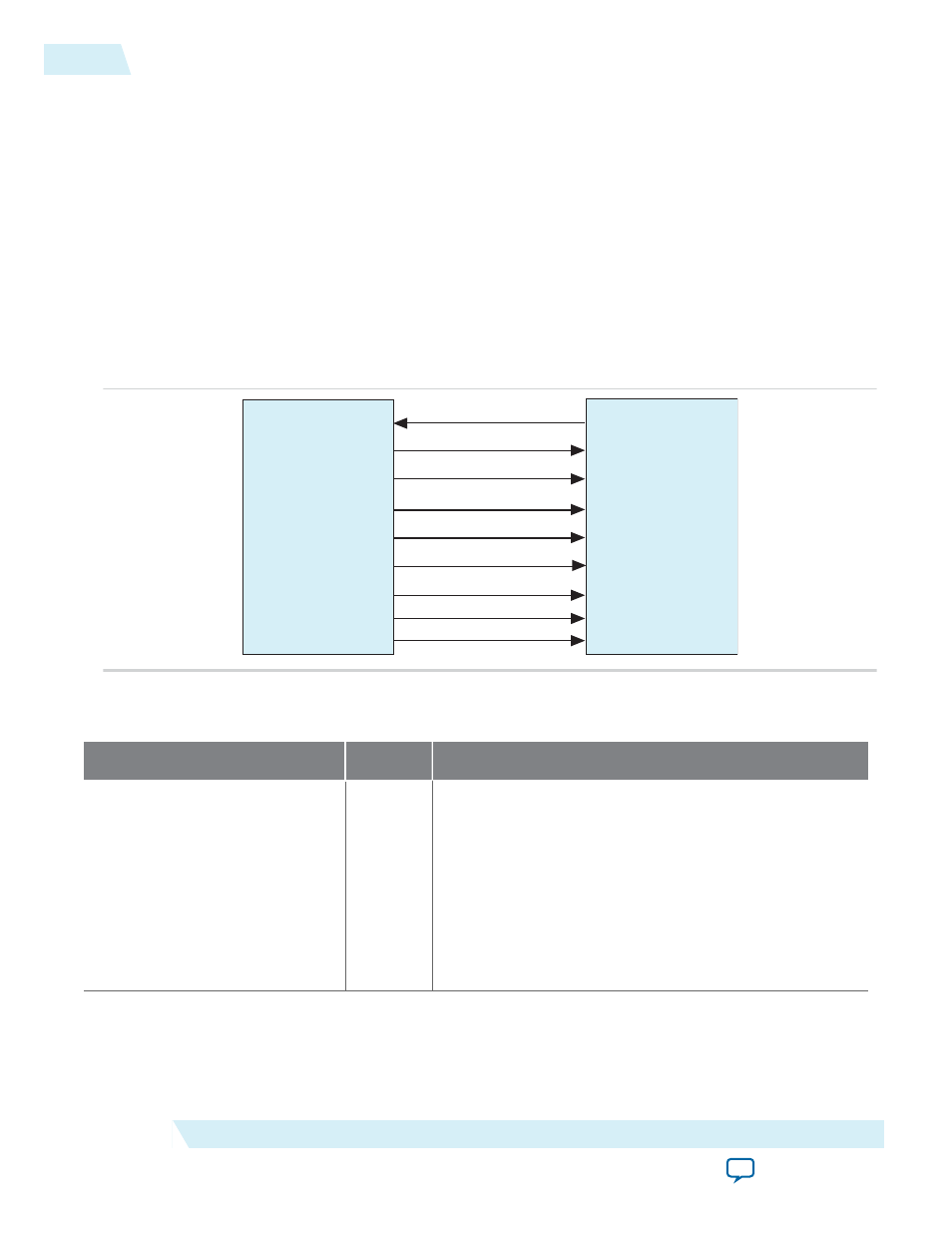

Figure 4-1: Application to HMC Controller IP Core

The client acts as a source and the HMC Controller acts as a sink in the transmit direction.

dp_req_ready

dp_req_valid

dp_req_tag[8:0]

dp_req_cmd[5:0]

dp_req_cube[2:0]

dp_req_addr[33:0]

dp_req_data[255:0] or [511:0]

dp_req_sop

dp_req_eop

HMC Controller

IP Core

TX Client

Logic

Table 4-1: Signals of the Data Path Request Interface

All interface signals are synchronous with the

core_clk

clock.

Signal Name

Direction

Description

dp_req_ready

Output

When the HMC Controller IP core asserts this signal, the

IP core is ready to receive data. The HMC Controller IP

core accepts data when both

dp_req_ready

and

dp_req_

valid

are asserted in the same cycle.

The IP core deasserts this signal to back-pressure the

application when it cannot currently process any

incoming requests.

The IP core does not deassert this signal between the

cycles of a multi-cycle write data transfer.

4-2

Application Request Interface

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Signals