Altera Hybrid Memory Cube Controller User Manual

Page 51

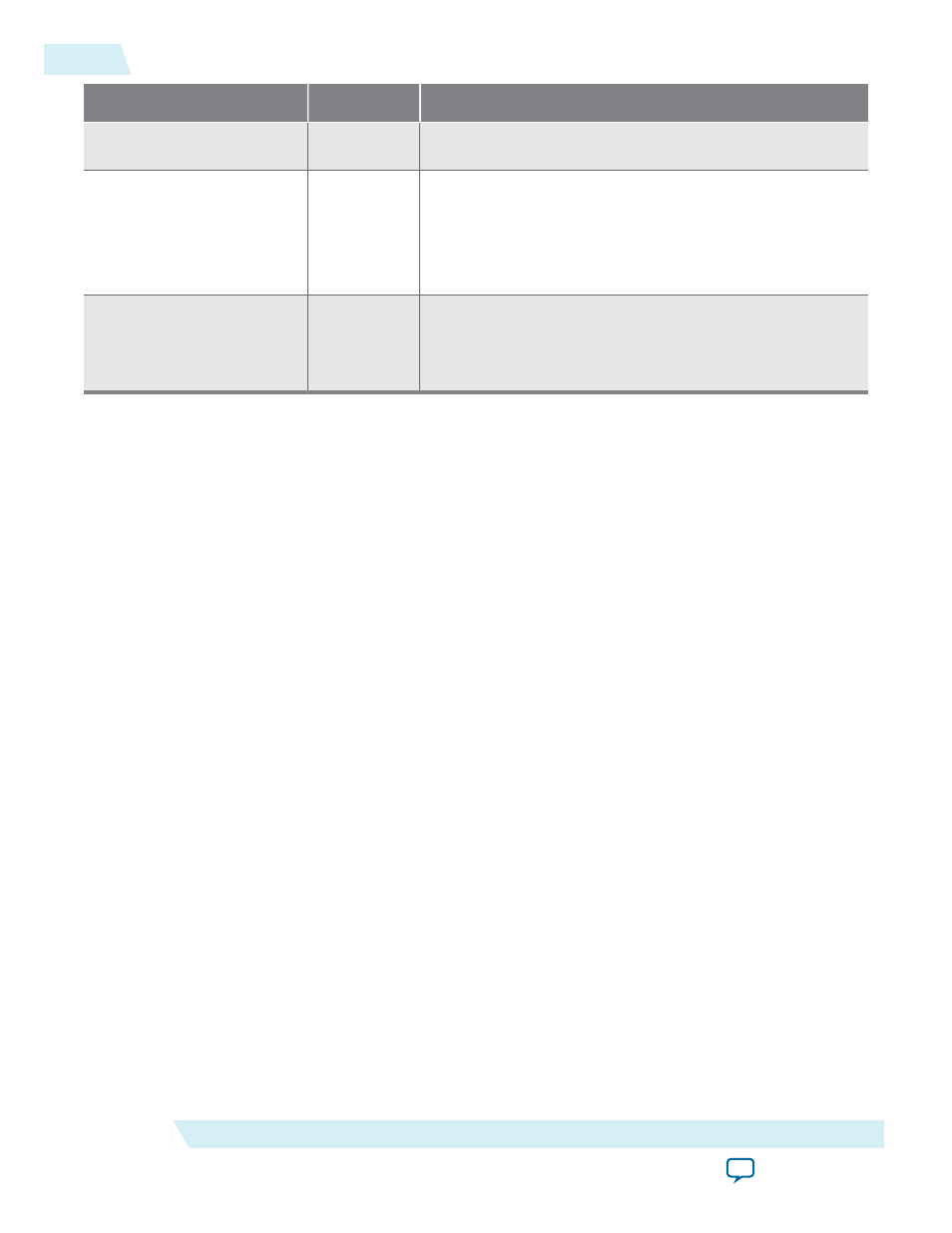

Signal Name

Direction

Description

reconfig_

writedata[31:0]

Input

Write data

reconfig_

readdata[31:0]

Output

Read data

The data on

reconfig_readdata[31:0]

is valid on the

rising edge of

reconfig_clk

following a clock cycle in

which

reconfig_read

is asserted and

reconfig_

waitrequest

is deasserted.

reconfig_waitrequest

Output

Indicates the IP core is not ready. You must maintain the

values on the input signals while

reconfig_waitrequest

is

asserted. The data on

reconfig_readdata[31:0]

is not

valid while

reconfig_waitrequest

is asserted.

Related Information

•

Transceiver Reconfiguration Interface

•

on page 3-8

•

For more information about the Avalon-MM protocol, including timing diagrams, refer to the Avalon

Memory-Mapped Interfaces chapter.

•

Information about the Arria 10 dynamic reconfiguration interface signals and the Arria 10 Native PHY

IP core hard PCS registers that you can program through the Arria 10 transceiver reconfiguration

interface. The HMC Controller IP core transceiver reconfiguration signals pass directly to the Arria 10

Native PHY IP core included in the HMC Controller IP core.

•

Detailed information about the Arria 10 transceiver registers.

4-14

Transceiver Reconfiguration Signals

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Signals