Altera Hybrid Memory Cube Controller User Manual

Page 62

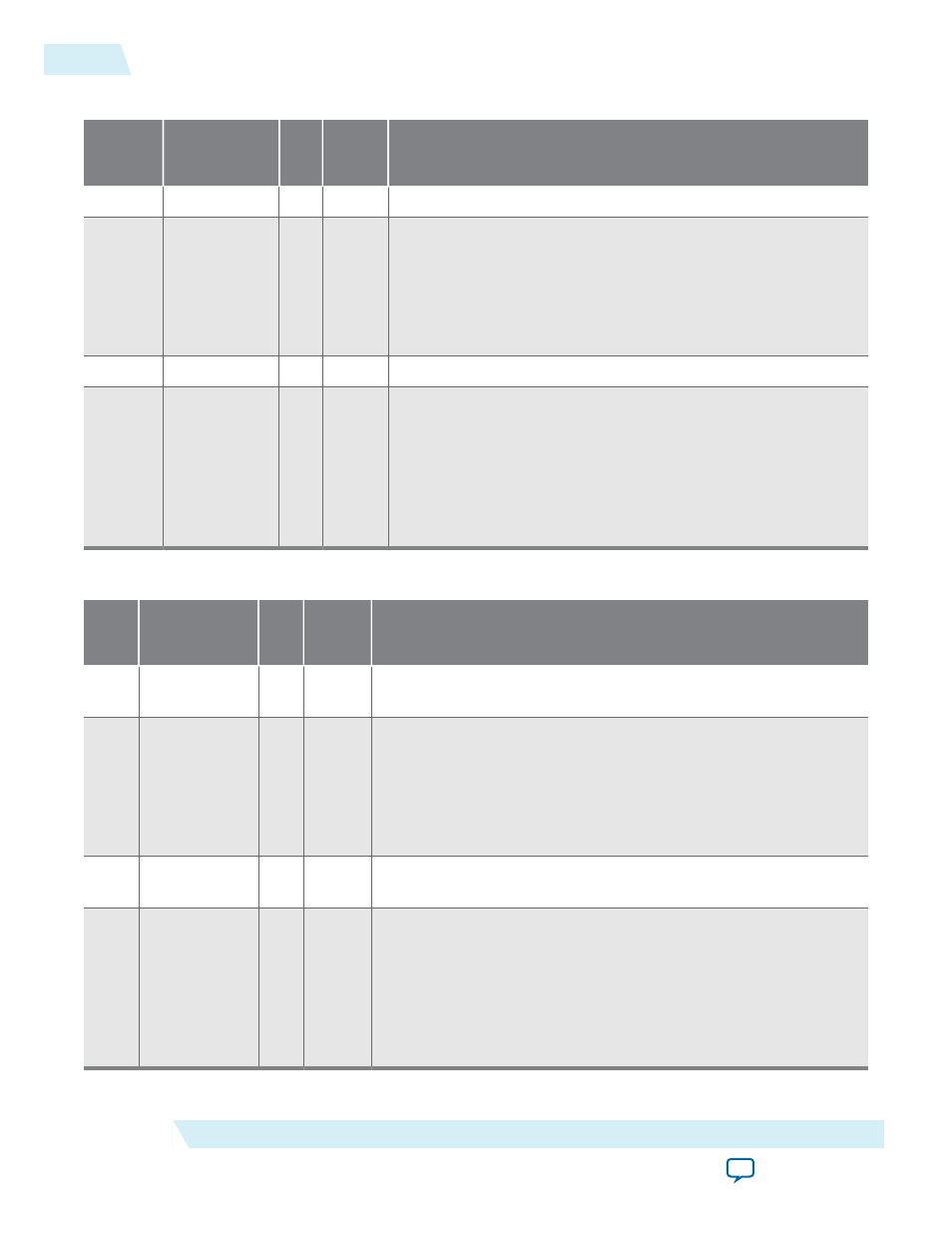

Table 5-13: HMC Controller IP Core RETRY_BUFFER_ECC_COUNT Register at Offset 0x38

Bits

Field Name

Typ

e

Value

on

Reset

Description

31:24 Reserved

RO 0x00

23:16

Uncorrectabl

e Count

RC 0x00

Number of uncorrectable ECC errors the IP core detected in the

Retry Buffer memory. This counter saturates at 0xFF.

This field maintains the value of zero unless you turn on Enable

M20K ECC support in the parameter editor.

Reading this register clears the

Uncorrectable Count

field.

15:8

Reserved

RO 0x00

7:0

Correctable

Count

RC 0x00

Number of correctable ECC errors the IP core detected in the

Retry Buffer memory (and corrected). This counter saturates at

0xFF.

This field maintains the value of zero unless you turn on Enable

M20K ECC support in the parameter editor.

Reading this register clears the

Correctable Count

field.

Table 5-14: HMC Controller IP Core RESPONSE_BUFFER_ECC_COUNT Register at Offset 0x3C

Bits

Field Name

Type

Value

on

Reset

Description

31:

24

Reserved

RO 0x00

23:

16

Uncorrectable

Count

RC

0x00

Number of uncorrectable ECC errors the IP core detected in the

Response Queue memory. This counter saturates at 0xFF.

This field maintains the value of zero unless you turn on Enable

M20K ECC support in the parameter editor.

Reading this register clears the

Uncorrectable Count

field.

15:

8

Reserved

RO 0x00

7:0

Correctable

Count

RC

0x00

Number of correctable ECC errors the IP core detected in the

Response Queue memory (and corrected). This counter saturates at

0xFF.

This field maintains the value of zero unless you turn on Enable

M20K ECC support in the parameter editor.

Reading this register clears the

Correctable Count

field.

5-10

Error and Retry Statistics Registers

UG-01152

2015.05.04

Altera Corporation

HMC Controller IP Core Register Map