Solvline Eddy DKV2.1.0.3 User Manual

Page 20

Chapter 2. Getting Started

20

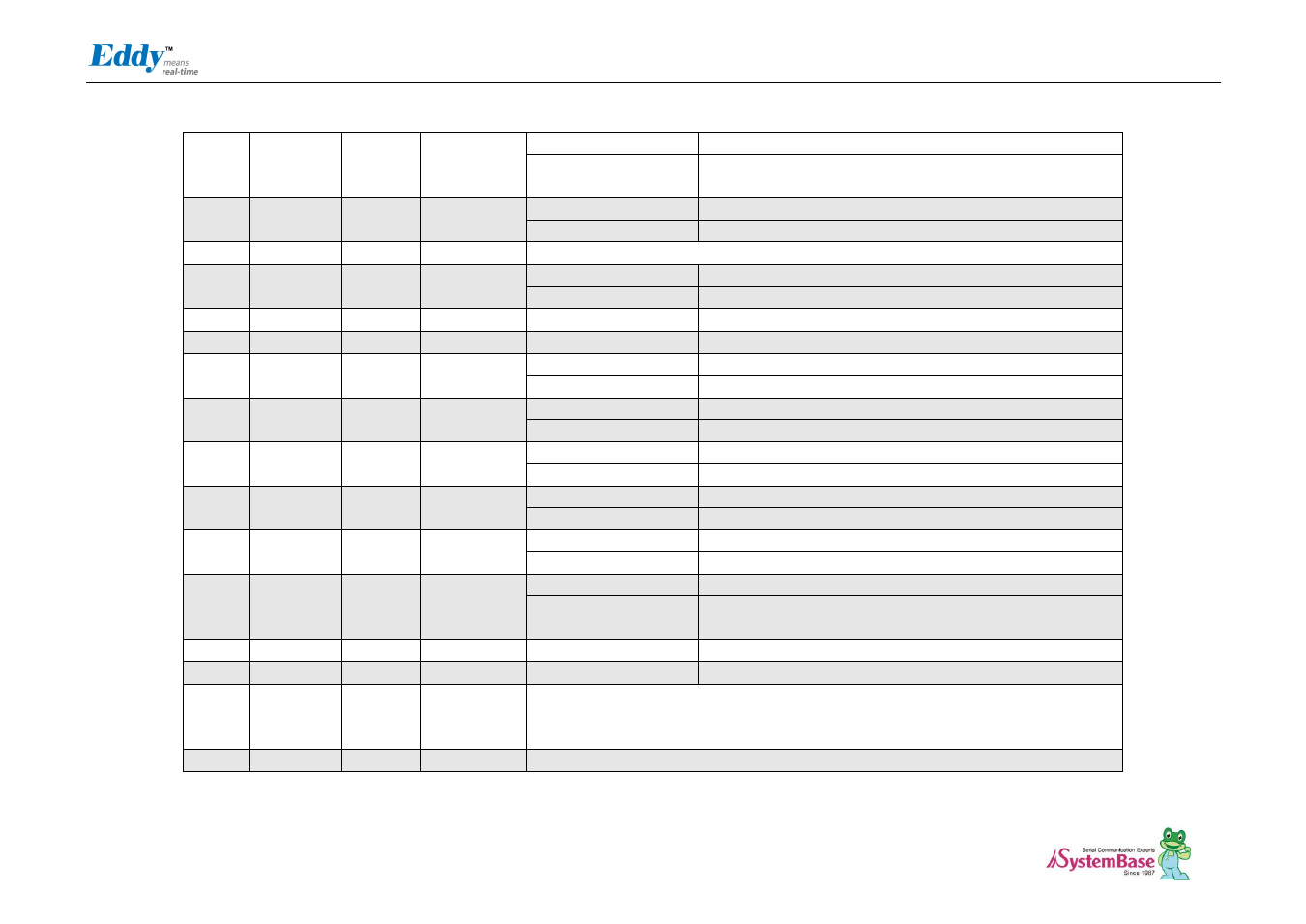

11

PC20

J8_11

J4_25

Peripheral A : D20

External Data Bus

Peripheral B :

SPI1_NPCS3

SPI1(Serial Peripheral Interface) Peripheral Chip Select 3

12

PC10

J8_12

J4_15

Peripheral A : A25

External Address Bus

Peripheral B : CTS3

USART3 Clear to Send

13

PA22

J8_13

-

Digital I/O Input 4

14

PC15

J8_14

J4_20

Peripheral A : NWAIT

External Wait Signal Input

Peripheral B : IRQ1

External Interrupt Input 2

15

PB8

J8_15

J2_9

Peripheral A : TXD2

UART2 Transmit Data

16

PB9

J8_16

J2_10

Peripheral A : RXD2

UART2 Receive Data

17

PB10

J8_17

J2_11

Peripheral A : TXD3

UART3 Transmit Data

Peripheral B : ISI_D8

Image Sensor Data 8

18

PB11

J8_18

J2_12

Peripheral A : RXD3

UART3 Receive Data

Peripheral B : ISI_D9

Image Sensor Data 9

19

PC0

J8_19

J4_7

Peripheral A : AD0

Analog to Digital Converter Input Ch0

Peripheral B : SCK3

USART3 Serial Clock

20

PC1

J8_20

J4_8

Peripheral A : AD1

Analog to Digital Converter Input Ch1

Peripheral B : PCK0

Programmable Clock Output 0

21

PC2

J8_21

J4_9

Peripheral A : AD2

Analog to Digital Converter Input Ch2

Peripheral B : PCK1

Programmable Clock Output 1

22

PC3

J8_22

J4_10

Peripheral A : AD3

Analog to Digital Converter Input Ch3

Peripheral B :

SPI1_NPCS3

SPI1(Serial Peripheral Interface) Peripheral Chip Select 3

23

PB14

J8_23

J2_15

Peripheral A : DRXD

Debug Receive Data

24

PB15

J8_24

J2_16

Peripheral A : DTXD

Debug Transmit Data

27

BMS

J8_27

-

Boot Mode Select signal

BMS = 1, Boot on Embedded ROM

BMS = 0, Boot on External Memory

28

NRST

J8_28

J1_20

External device Reset signal, active low signal