Programming platform flash prom via usb, Generating the fpga configuration bitstream file, Figure 4-9 – Digilent 410-087P-KIT User Manual

Page 31

Spartan-3E Starter Kit Board User Guide

31

UG230 (v1.0) March 9, 2006

Programming the FPGA, CPLD, or Platform Flash PROM via USB

R

Programming Platform Flash PROM via USB

The on-board USB-JTAG circuitry also programs the Xilinx XCF04S serial Platform Flash

PROM. The steps provided in this section describe how to set up the PROM file and how

to download it to the board to ultimately program the FPGA.

Generating the FPGA Configuration Bitstream File

Before generating the PROM file, create the FPGA bitstream file. The FPGA provides an

output clock, CCLK, when loading itself from an external PROM. The FPGA’s internal

CCLK oscillator always starts at its slowest setting, approximately 1.5 MHz. Most external

PROMs support a higher frequency. Increase the CCLK frequency as appropriate to reduce

the FPGA’s configuration time. The Xilinx XCF04S Platform Flash supports a 25 MHz

CCLK frequency.

Right-click Generator Programming File in the Processes pane, as shown in

. Left-click Properties.

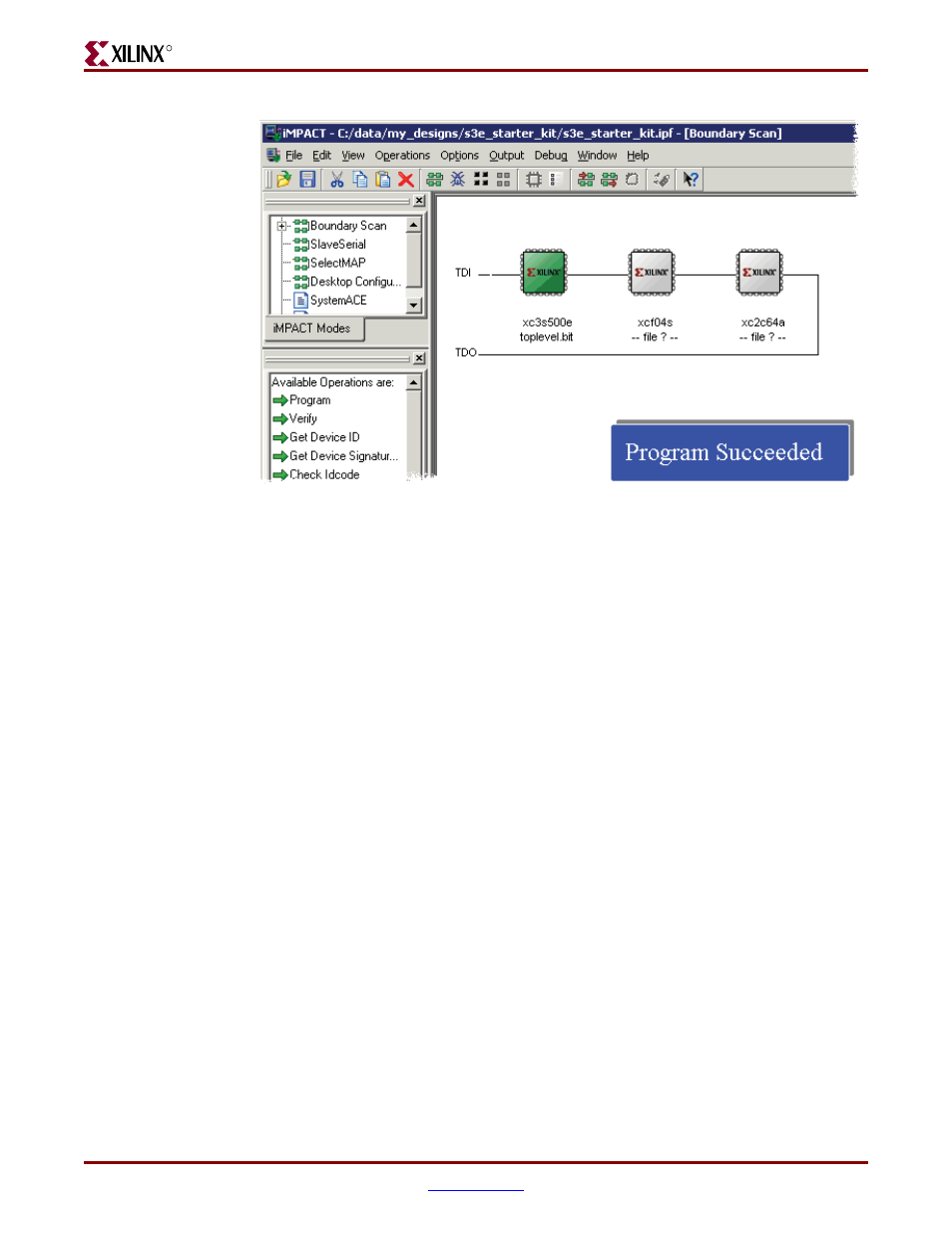

Figure 4-9:

iMPACT Programming Succeeded, the FPGA’s DONE Pin is High

UG230_c4_10_022406