Microblaze ethernet ip cores – Digilent 410-087P-KIT User Manual

Page 111

Spartan-3E Starter Kit Board User Guide

111

UG230 (v1.0) March 9, 2006

MicroBlaze Ethernet IP Cores

R

MicroBlaze Ethernet IP Cores

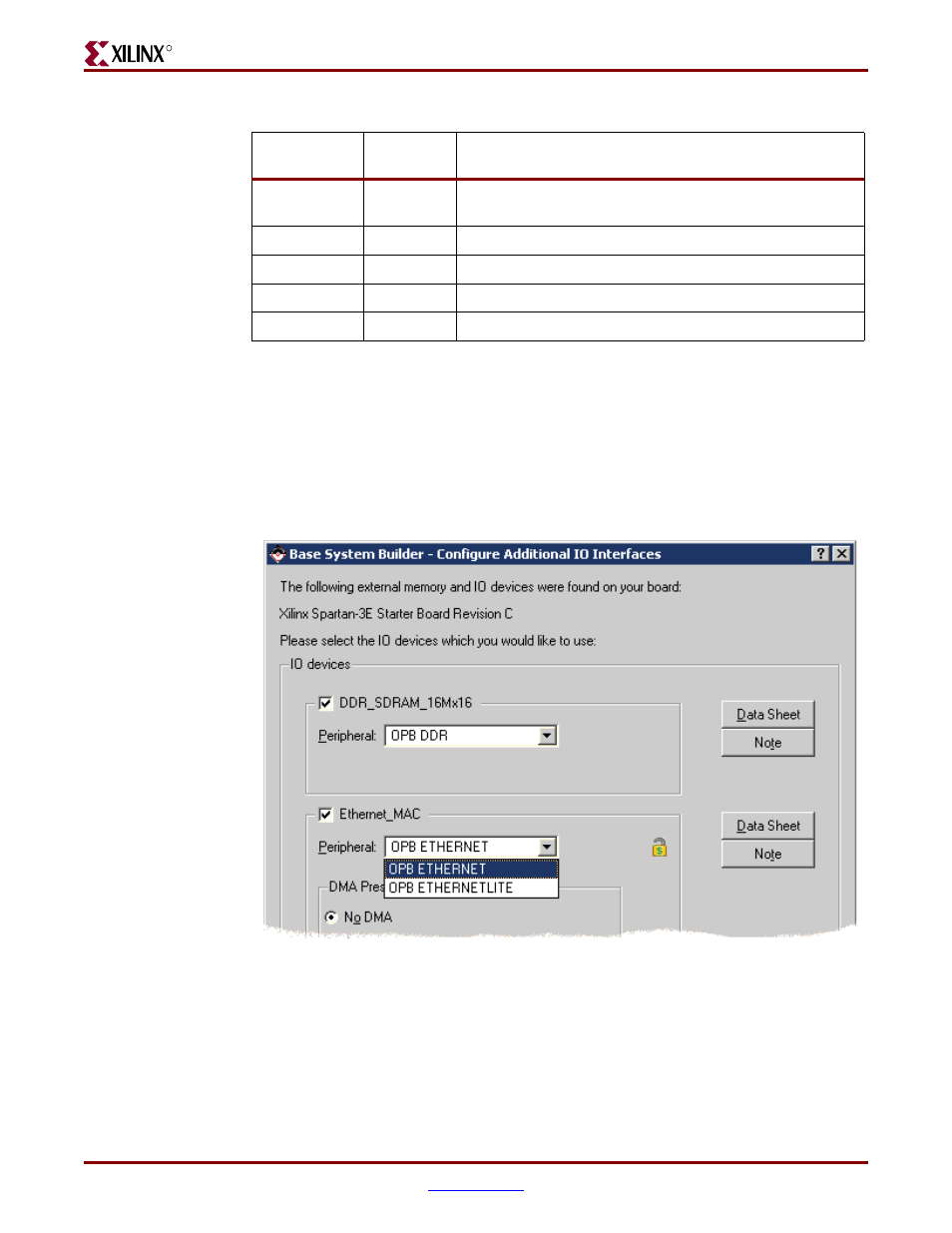

The Ethernet PHY is primarily intended for use with MicroBlaze applications. As such, an

Ethernet MAC is part of the EDK Platform Studio’s Base System Builder. Both the full

Ethernet MAC and the Lite version are available for evaluation, as shown in

.

The Ethernet Lite MAC controller core uses fewer FPGA resources and is ideal for

applications that do not require support for interrupts, back-to-back data transfers, and

statistics counters.

The Ethernet MAC core requires design constraints to meet the required performance.

Refer to the OPB Ethernet MAC data sheet (v1.02) for details. The OPB bus clock frequency

must be 65 MHz or higher for 100 Mbps Ethernet operations and 6.5 MHz or faster for

10 Mbps Ethernet operations.

E_RX_CLK

V3

Receive Clock. 25 MHz in 100Base-TX mode, and 2.5 MHz in

10Base-T mode.

E_CRS

U13

Carrier Sense

E_COL

U6

MII Collision Detect.

E_MDC

P9

Management Clock. Serial management clock.

E_MDIO

U5

Management Data Input/Output.

Table 14-1:

FPGA Connections to the LAN83C185 Ethernet PHY

(Continued)

Signal Name

FPGA Pin

Number

Function

Figure 14-3:

Ethernet MAC IP Cores for the Spartan-3E Starter Kit Board

UG230_c14_03_022706