Header j4, Ucf location constraints – Digilent 410-087P-KIT User Manual

Page 122

122

Spartan-3E Starter Kit Board User Guide

UG230 (v1.0) March 9, 2006

Chapter 15: Expansion Connectors

R

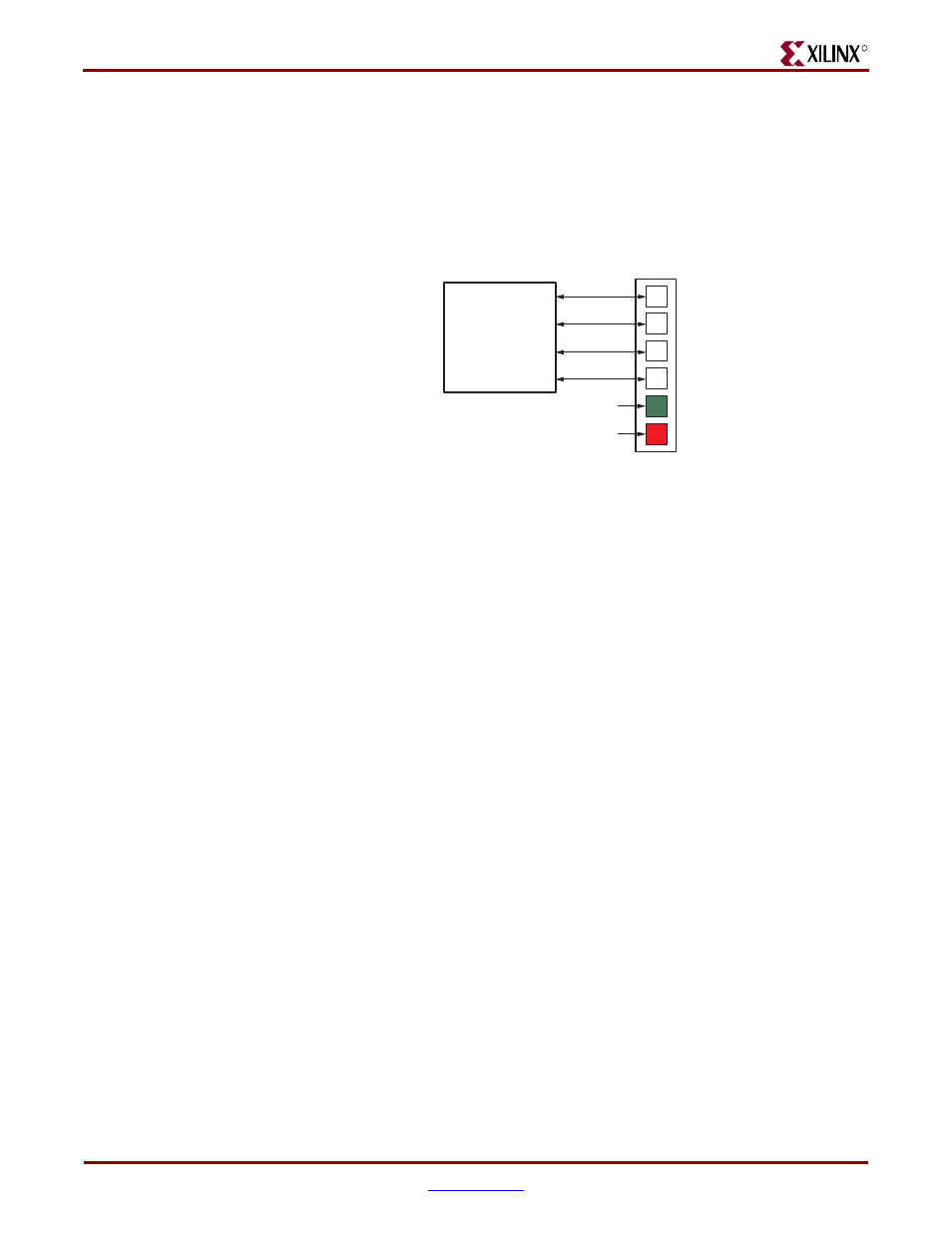

Header J4

The J4 header, shown in

, is located immediately to the left of the J1 header. It

uses a 6-pin header consisting of 0.1-inch centered stake pins. Four FPGA pins connect to

the J4 header, FX2_IO<12:9>. These four signals are also shared with the Hirose FX2

connector. The board supplies 3.3V to the accessory board mounted in the J4 socket on the

bottom pin.

UCF Location Constraints

provides the User Constraint File (UCF) constraints for accessory headers,

including the I/O pin assignment and the I/O standard used. These header connections

are shared with the FX2 connector, as shown in

.

Figure 15-10:

FPGA Connections to the J4 Accessory Header

J4

(D7)

FX2_IO9

(C7)

FX2_IO10

(F8)

(E8)

Spartan-3E FPGA

GND

3.3V

FX2_IO11

FX2_IO12

UG230_c12_09_022406

Figure 15-11:

UCF Location Constraints for Accessory Headers

# ==== 6-pin header J1 ====

# These four connections are shared with the FX2 connector

#

NET

"J1<0>"

LOC

= "B4" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J1<1>"

LOC

= "A4" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J1<2>"

LOC

= "D5" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J1<3>"

LOC

= "C5" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

# ==== 6-pin header J2 ====

# These four connections are shared with the FX2 connector

#

NET

"J2<0>"

LOC

= "A6" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J2<1>"

LOC

= "B6" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J2<2>"

LOC

= "E7" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J2<3>"

LOC

= "F7" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

# ==== 6-pin header J4 ====

# These four connections are shared with the FX2 connector

#

NET

"J4<0>"

LOC

= "D7" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J4<1>"

LOC

= "C7" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J4<2>"

LOC

= "F8" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;

#

NET

"J4<3>"

LOC

= "E8" |

IOSTANDARD

= LVTTL |

SLEW

= SLOW |

DRIVE

= 6 ;