Configuration mode jumpers, Figure 4-2 – Digilent 410-087P-KIT User Manual

Page 26

26

Spartan-3E Starter Kit Board User Guide

UG230 (v1.0) March 9, 2006

Chapter 4: FPGA Configuration Options

R

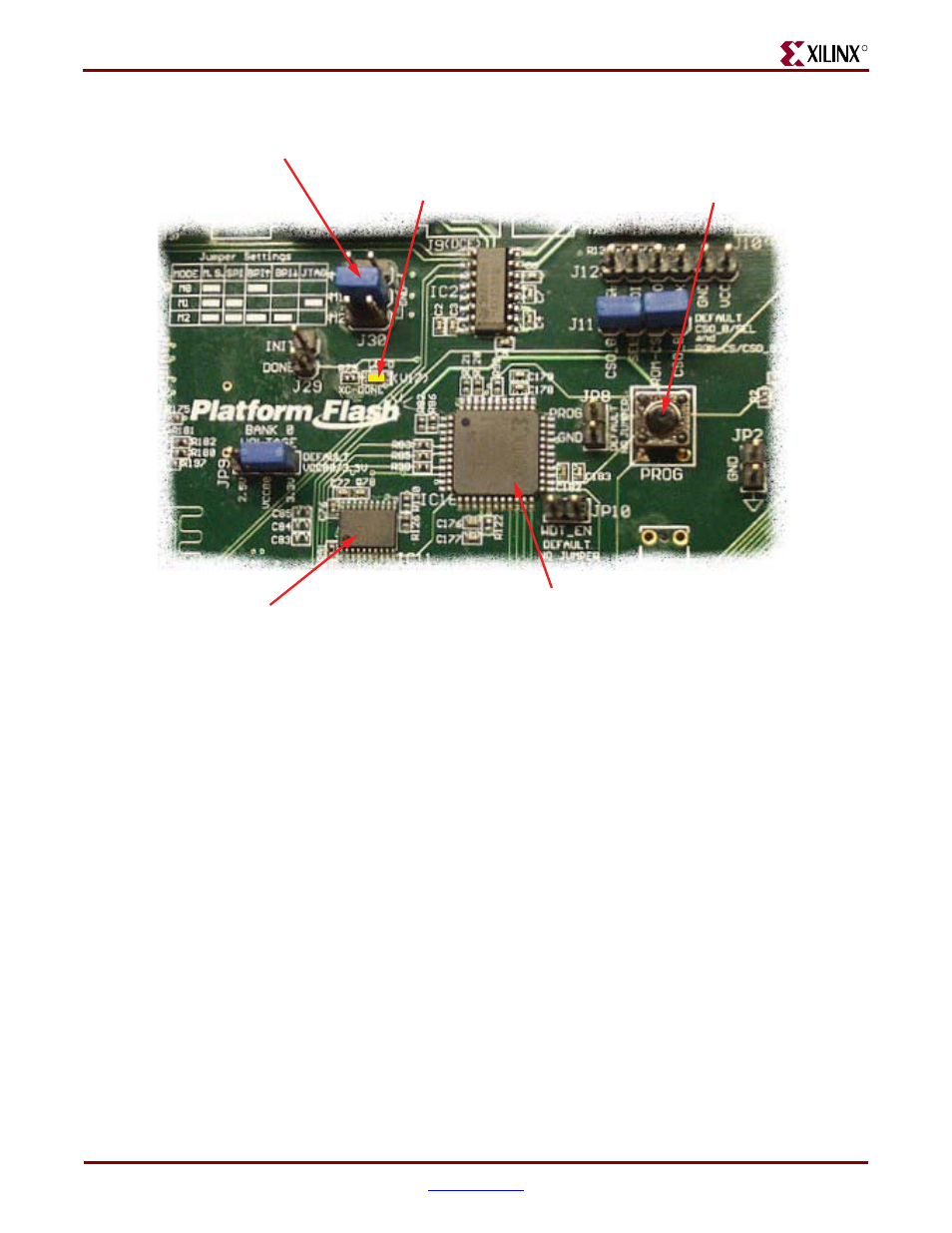

The configuration mode jumpers determine which configuration mode the FPGA uses

when power is first applied, or whenever the PROG button is pressed.

The DONE pin LED lights when the FPGA successfully finishes configuration.

Pressing the PROG button forces the FPGA to restart its configuration process.

The 4 Mbit Xilinx Platform Flash PROM provides easy, JTAG-programmable configuration

storage for the FPGA. The FPGA configures from the Platform Flash using Master Serial

mode.

The 64-macrocell XC2C64A CoolRunner II CPLD provides additional programming

capabilities and flexibility when using the BPI Up, BPI Down, or MultiBoot configuration

modes and loading the FPGA from the StrataFlash parallel Flash PROM. The CPLD is user-

programmable.

Configuration Mode Jumpers

As shown in

, the J30 jumper block settings control the FPGA’s configuration

mode. Inserting a jumper grounds the associated mode pin. Insert or remove individual

jumpers to select the FPGA’s configuration mode and associated configuration memory

source.

Figure 4-2:

Detailed Configuration Options

4 Mbit Xilinx Platform Flash PROM

PROG_B Push Button Switch

Configuration Mode Jumper Settings (Header J30)

64 Macrocell Xilinx XC2C64A CoolRunner CPLD

Select between three on-board configuration sources

DONE Pin LED

Lights up when FPGA successfully configured

Press and release to restart configuration

Configuration storage for Master Serial mode

Controller upper address lines in BPI mode and

Platform Flash chip select (User programmable)

UG230_c4_02_030906