Serial downloading, Atmega16(l) – Rainbow Electronics ATmega64L User Manual

Page 265

265

ATmega16(L)

2466B–09/01

Notes:

1. t

WLRH

is valid for the Write Flash, Write EEPROM, Write Fuse Bits and Write Lock

Bits commands.

2. t

WLRH_CE

is valid for the Chip Erase command.

Serial Downloading

Both the Flash and EEPROM memory arrays can be programmed using the serial SPI

bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI

(input) and MISO (output). After RESET is set low, the Programming Enable instruction

needs to be executed first before program/erase operations can be executed. NOTE, in

Table 114 on page 266, the pin mapping for SPI programming is listed. Not all parts use

the SPI pins dedicated for the internal SPI interface.

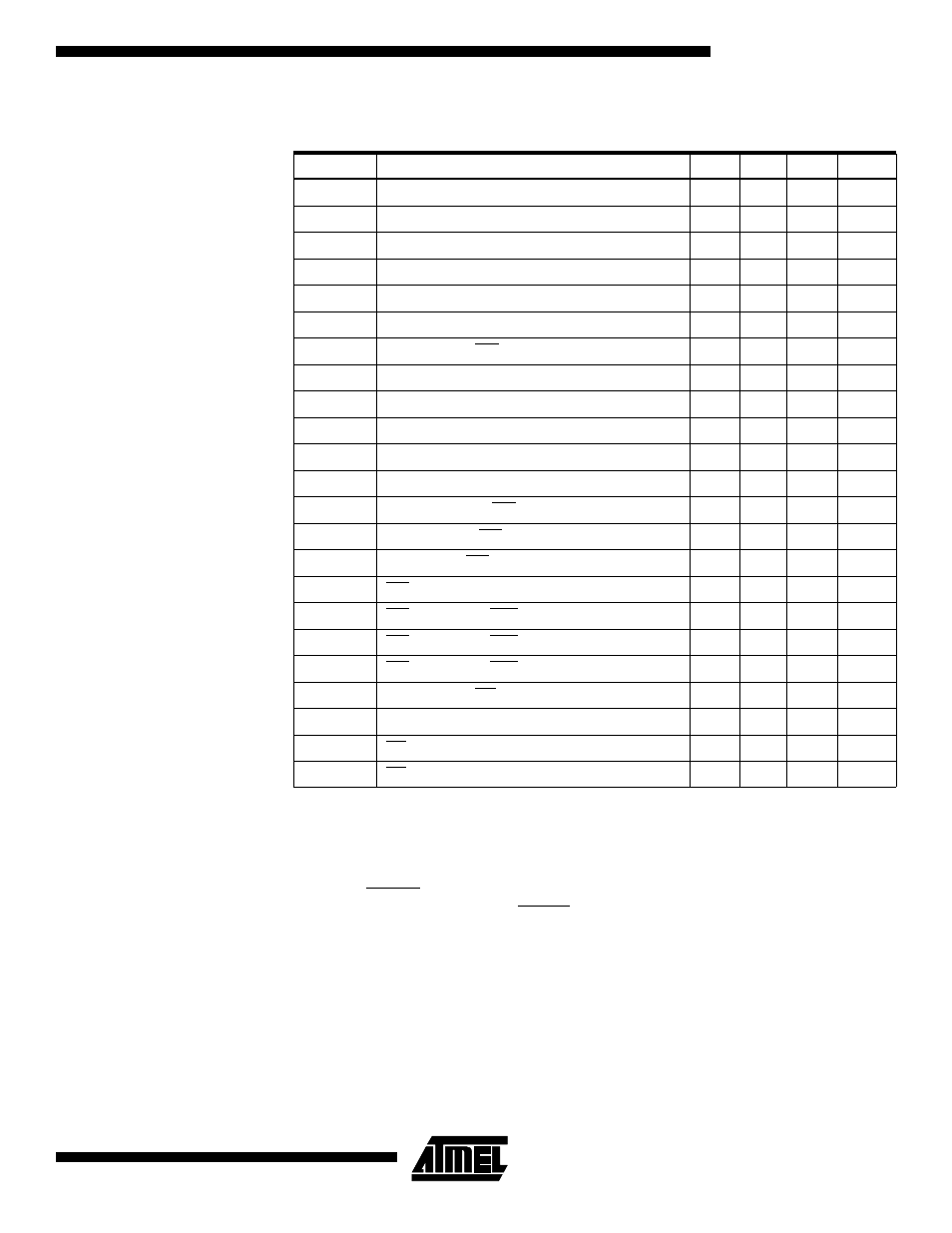

Table 113. Parallel Programming Characteristics, V

CC

= 5 V ± 10%

Symbol

Parameter

Min

Typ

Max

Units

V

PP

Programming Enable Voltage

11.5

12.5

V

I

PP

Programming Enable Current

250

µA

t

DVXH

Data and Control Valid before XTAL1 High

67

ns

t

XLXH

XTAL1 Low to XTAL1 High

200

ns

t

XHXL

XTAL1 Pulse Width High

150

ns

t

XLDX

Data and Control Hold after XTAL1 Low

67

ns

t

XLWL

XTAL1 Low to WR Low

0

ns

t

XLPH

XTAL1 Low to PAGEL high

0

ns

t

PLXH

PAGEL low to XTAL1 high

150

ns

t

BVPH

BS1 Valid before PAGEL High

67

ns

t

PHPL

PAGEL Pulse Width High

150

ns

t

PLBX

BS1 Hold after PAGEL Low

67

ns

t

WLBX

BS2/1 Hold after WR Low

67

ns

t

PLWL

PAGEL Low to WR Low

67

ns

t

BVWL

BS1 Valid to WR Low

67

ns

t

WLWH

WR Pulse Width Low

150

ns

t

WLRL

WR Low to RDY/BSY Low

0

1

µs

t

WLRH

WR Low to RDY/BSY High

3.7

4.5

ms

t

WLRH_CE

WR Low to RDY/BSY High for Chip Erase

7.5

9

ms

t

XLOL

XTAL1 Low to OE Low

0

ns

t

BVDV

BS1 Valid to DATA valid

0

250

ns

t

OLDV

OE Low to DATA Valid

250

ns

t

OHDZ

OE High to DATA Tri-stated

250

ns