Timer/counter interrupt mask register – timsk, Timer/counter interrupt flag register – tifr, Atmega16(l) – Rainbow Electronics ATmega64L User Manual

Page 126

126

ATmega16(L)

2466B–09/01

unpredictable, as it depends on the wake-up time. The recommended procedure for

reading TCNT2 is thus as follows:

1.

Write any value to either of the registers OCR2 or TCCR2.

2.

Wait for the corresponding Update Busy Flag to be cleared.

3.

Read TCNT2.

•

During asynchronous operation, the synchronization of the interrupt flags for the

asynchronous timer takes 3 processor cycles plus one timer cycle. The timer is

therefore advanced by at least one before the processor can read the timer value

causing the setting of the interrupt flag. The output compare pin is changed on the

timer clock and is not synchronized to the processor clock.

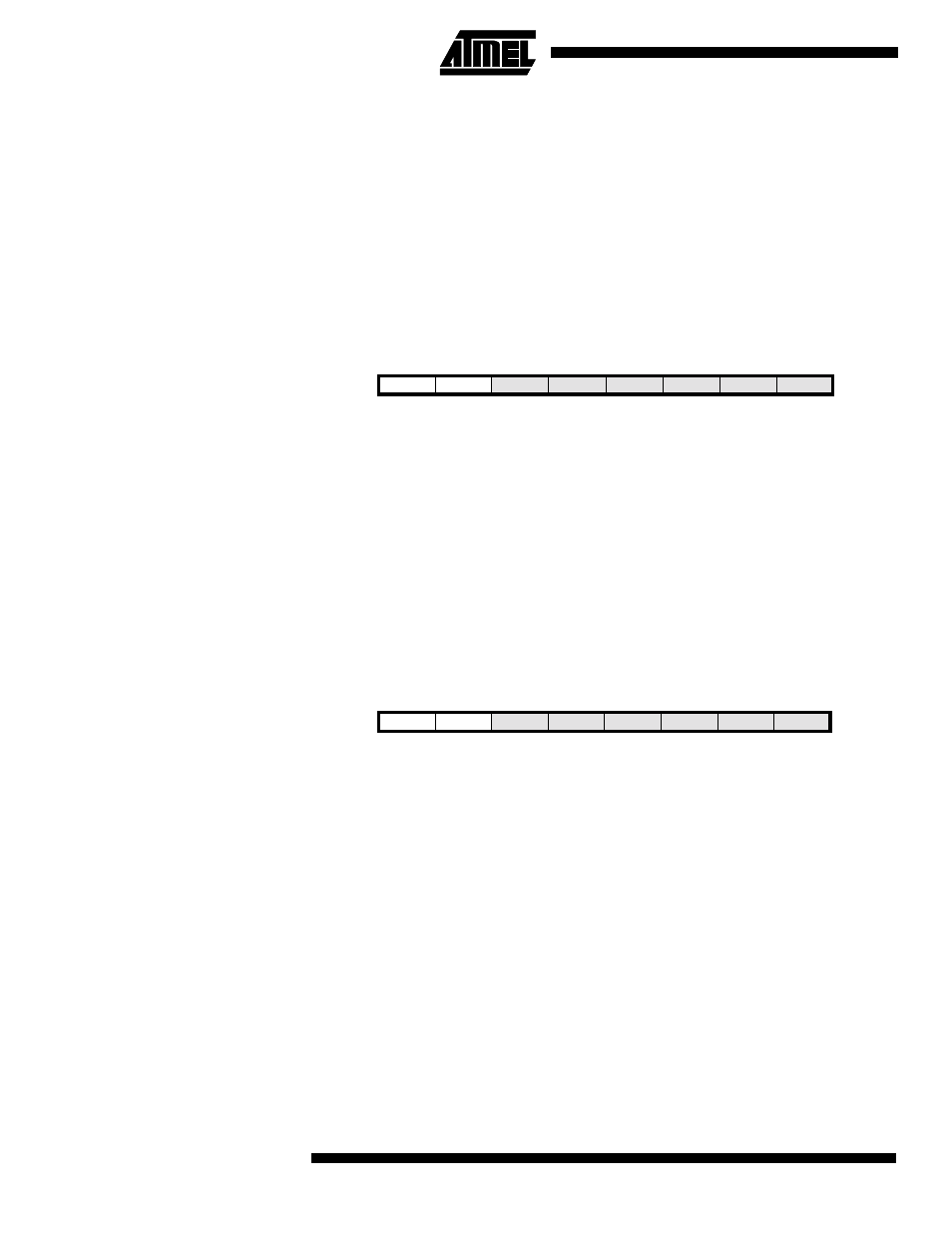

Timer/Counter Interrupt Mask

Register – TIMSK

• Bit 7 - OCIE2: Timer/Counter2 Output Compare Match Interrupt Enable

When the OCIE2 bit is written to one and the I-bit in the Status Register is set (one), the

Timer/Counter2 Compare Match interrupt is enabled. The corresponding interrupt is

executed if a compare match in Timer/Counter2 occurs, i.e., when the OCF2 bit is set in

the Timer/Counter Interrupt Flag Register - TIFR.

• Bit 6 - TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the Status Register is set (one), the

Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if

an overflow in Timer/Counter2 occurs, i.e., when the TOV2 bit is set in the

Timer/Counter Interrupt Flag Register - TIFR.

Timer/Counter Interrupt Flag

Register – TIFR

• Bit 7 - OCF2: Output Compare Flag 2

The OCF2 bit is set (one) when a compare match occurs between the Timer/Counter2

and the data in OCR2 - Output Compare Register2. OCF2 is cleared by hardware when

executing the corresponding interrupt handling vector. Alternatively, OCF2 is cleared by

writing a logic one to the flag. When the I-bit in SREG, OCIE2 (Timer/Counter2 Com-

pare match Interrupt Enable), and OCF2 are set (one), the Timer/Counter2 Compare

match Interrupt is executed.

• Bit 6 - TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared

by hardware when executing the corresponding interrupt handling vector. Alternatively,

TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE2

(Time r/Cou nter2 Ove rf lo w In terrupt Enab le), and TOV2 a re set (one ), th e

Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when

Timer/Counter2 changes counting direction at $00.

Bit

7

6

5

4

3

2

1

0

OCIE2

TOIE2

TICIE1

OCIE1A

OCIE1B

TOIE1

OCIE0

TOIE0

TIMSK

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

OCF2

TOV2

ICF1

OCF1A

OCF1B

TOV1

OCF0

TOV0

TIFR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0