Sample_preload; $2, Avr_reset; $c, Bypass; $f – Rainbow Electronics ATmega64L User Manual

Page 223: Boundary-scan related register in i/o memory, Mcu control and status register – mcucsr, Atmega16(l)

223

ATmega16(L)

2466B–09/01

SAMPLE_PRELOAD; $2

Mandatory JTAG instruction for pre-loading the output latches and talking a snap-shot of

the input/output pins without affecting the system operation. However, the output latches

are not connected to the pins. The Boundary-scan Chain is selected as Data Register.

The active states are:

•

Capture-DR: Data on the external pins are sampled into the Boundary-scan Chain.

•

Shift-DR: The Boundary-scan Chain is shifted by the TCK input.

•

Update-DR: Data from the Boundary-scan Chain is applied to the output latches.

However, the output latches are not connected to the pins.

AVR_RESET; $C

The AVR specific public JTAG instruction for forcing the AVR device into the Reset

Mode or releasing the JTAG reset source. The TAP controller is not reset by this instruc-

tion. The one bit Reset Register is selected as Data Register. Note that the reset will be

active as long as there is a logic 'one' in the Reset Chain. The output from this chain is

not latched.

The active states are:

•

Shift-DR: The Reset Register is shifted by the TCK input.

BYPASS; $F

Mandatory JTAG instruction selecting the Bypass Register for Data Register.

The active states are:

•

Capture-DR: Loads a logic “0” into the Bypass Register.

•

Shift-DR: The Bypass Register cell between TDI and TDO is shifted.

Boundary-scan Related

Register in I/O Memory

MCU Control and Status

Register – MCUCSR

The MCU Control and Status Register contains control bits for general MCU functions,

and provides information on which reset source caused an MCU reset.

• Bits 7 - JTD: JTAG Interface Disable

When this bit is zero, the JTAG interface is enabled if the JTAGEN fuse is programmed.

If this bit is one, the JTAG interface is disabled. In order to avoid unintentional disabling

or enabling of the JTAG interface, a timed sequence must be followed when changing

this bit: The application software must write this bit to the desired value twice within four

cycles to change its value.

• Bit 4 - JTRF: JTAG Reset Flag

This bit is set if a reset is being caused by a logic one in the JTAG Reset Register

selected by the JTAG instruction AVR_RESET. This bit is reset by a Power-on reset, or

by writing a logic zero to the flag.

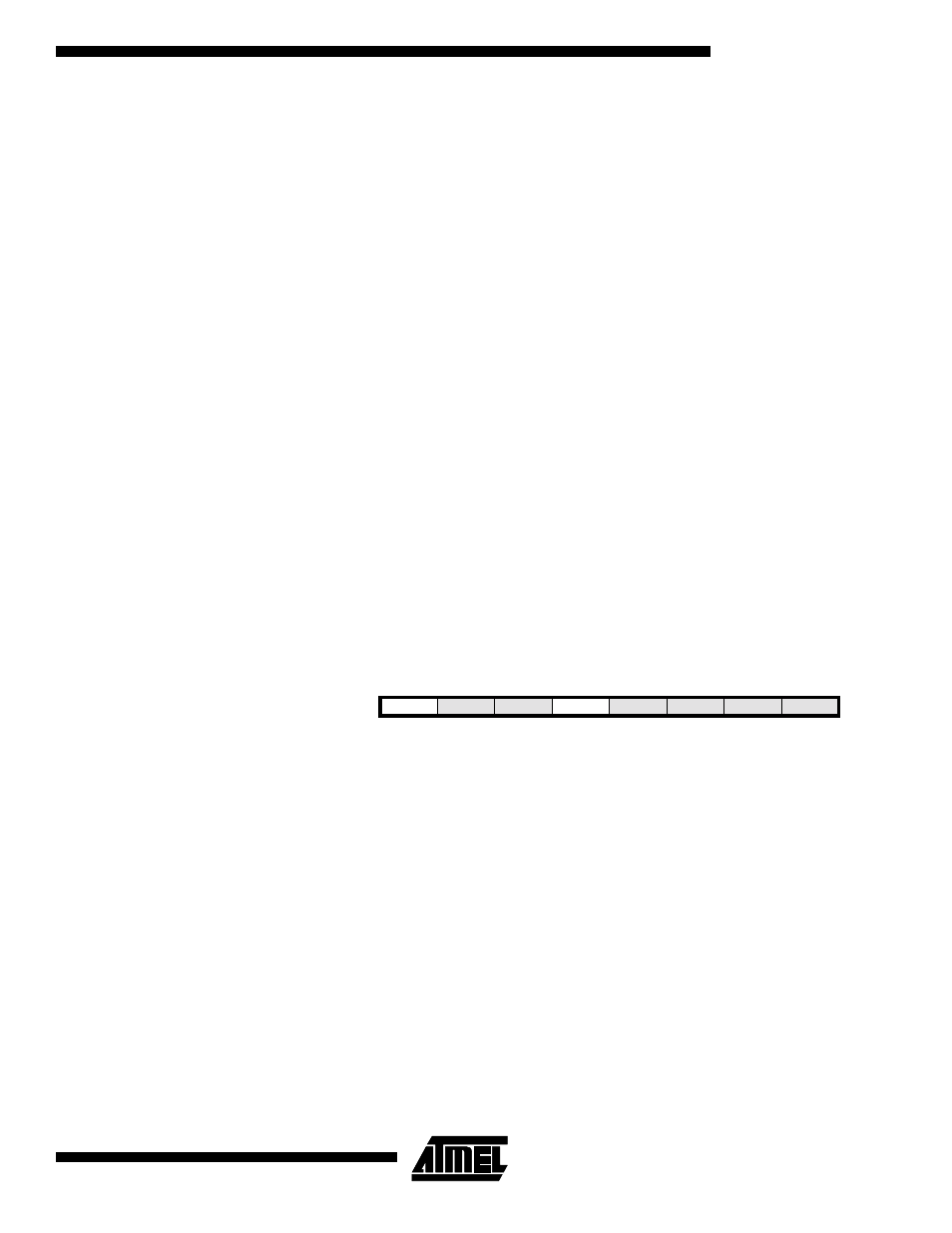

Bit

7

6

5

4

3

2

1

0

JTD

ISC2

–

JTRF

WDRF

BORF

EXTRF

PORF

MCUCSR

Read/Write

R/W

R/W

R

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

See Bit Description