Atmega16(l) – Rainbow Electronics ATmega64L User Manual

Page 103

103

ATmega16(L)

2466B–09/01

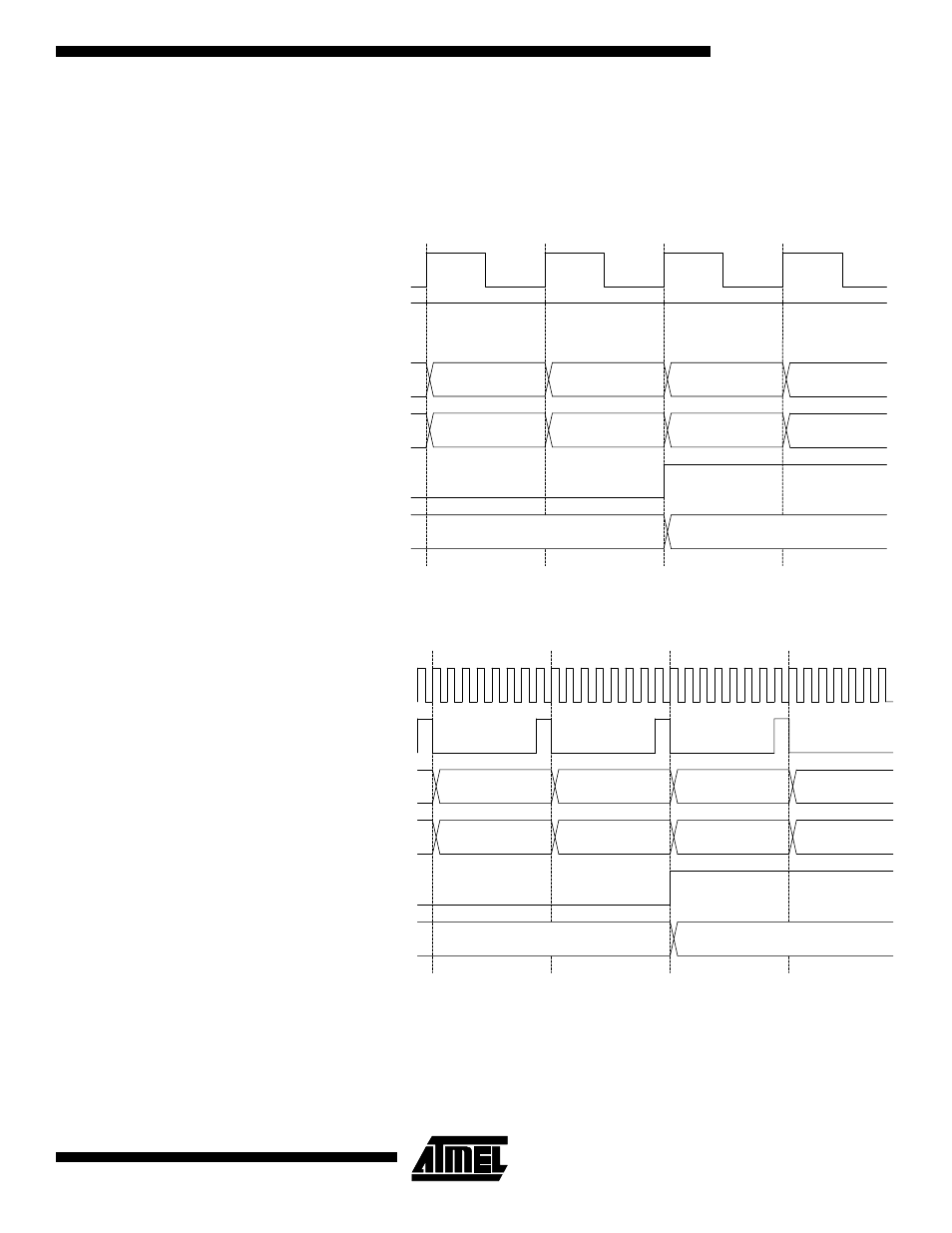

Figure 51 shows the count sequence close to TOP in various modes. When using phase

and frequency correct PWM mode the OCR1x register is updated at BOTTOM. The tim-

ing diagrams will be the same, but TOP should be replaced by BOTTOM, TOP-1 by

BOTTOM+1 and so on. The same renaming applies for modes that set the TOV1 flag at

BOTTOM.

Figure 51. Timer/Counter Timing Diagram, no Prescaling

Figure 52 shows the same timing data, but with the prescaler enabled.

Figure 52. Timer/Counter Timing Diagram, with Prescaler (f

clk_I/O

/8)

TOVn

(FPWM)

and ICFn

(if used

as TOP)

OCRnx

(Update at TOP)

TCNTn

(CTC and FPWM)

TCNTn

(PC and PFC PWM)

TOP - 1

TOP

TOP - 1

TOP - 2

Old OCRnx Value

New OCRnx Value

TOP - 1

TOP

BOTTOM

BOTTOM + 1

clk

Tn

(clk

I/O

/1)

clk

I/O

TOVn

(FPWM)

and ICFn

(if used

as TOP)

OCRnx

(Update at TOP)

TCNTn

(CTC and FPWM)

TCNTn

(PC and PFC PWM)

TOP - 1

TOP

TOP - 1

TOP - 2

Old OCRnx Value

New OCRnx Value

TOP - 1

TOP

BOTTOM

BOTTOM + 1

clk

I/O

clk

Tn

(clk

I/O

/8)

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)