Digital cmos dc characteristics – Rainbow Electronics AT86RF211 User Manual

Page 42

42

AT86RF211

1942C–WIRE–06/02

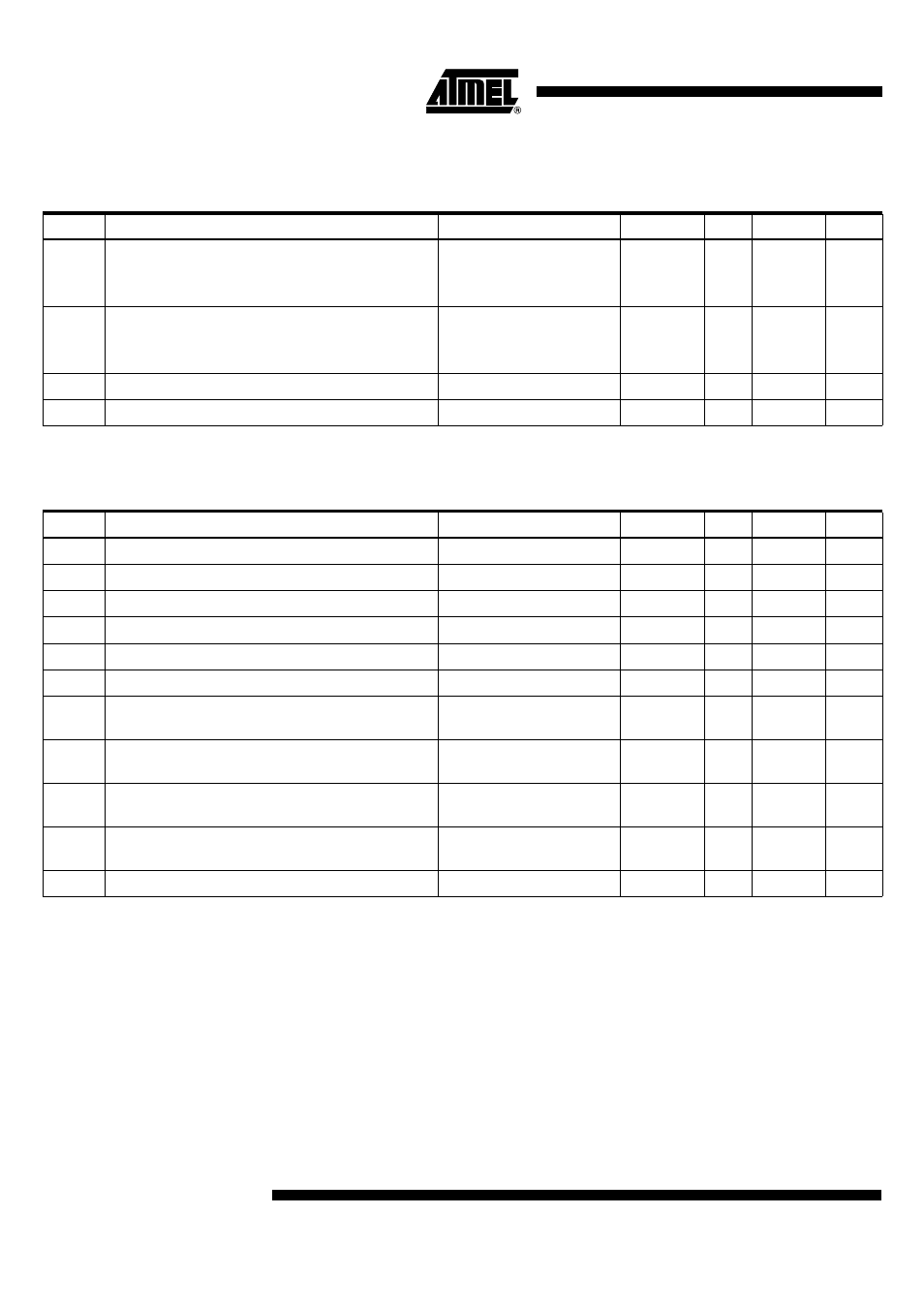

Digital CMOS DC

Characteristics

Unless otherwise specified, data is given for T = 25°C, V

SUPPLY

= 2.7V

Note:

1. For digital CMOS pins : SDATA, DATAMSG, DATACLK, WAKEUP.

2. For digital CMOS pins: SLE, SCK, SDATA

3. For digital CMOS pins: DATAMSG

Note:

These timings refer to the Figure 33 on page 25.

Name

Parameter

Conditions

Min

Typ

Max

Units

Vil

CMOS low level input voltage

- Normal input

- Schmitt trigger input

0.3*Vcc

0.2*Vcc

V

V

Vih

CMOS high level input voltage

- Normal input

- Schmitt trigger input

0.7*Vcc

0.85*Vcc

V

V

Vol

CMOS low level output voltage

Iol = 1 mA

0.2*Vcc

V

Voh

CMOS high level output voltage

Ioh = - 1 mA

0.8*Vcc

V

•

Timings

Name

Parameter

Conditions

Min

Typ

Max

Units

tr = tf

CMOS rise/fall times

C

L

= 50 pF ; 20% to 80%

30

ns

F

SCK frequency

0

5

MHz

T

SCK period

200

ns

tw

SCK low or high time

60

ns

tsd

SDATA setup before SCK rising

40

ns

thd

SDATA hold after SCK rising

40

ns

tpd

SDATA output propagation delay after SCK falling

(read mode) (C

L

= 30 pF)

2

50

ns

tpzon

Delay to switch SDATA to output after SCK falling

(read mode)

3

50

ns

tdle

Minimum delay between an edge of SLE and an

edge of SCK

40

ns

tpzd

Delay to switch SDATA to input (tri-state) after SLE

rising (read mode)

40

ns

C

Max load for CMOS output pins

50

pF