Dtr register – Rainbow Electronics AT86RF211 User Manual

Page 34

34

AT86RF211

1942C–WIRE–06/02

DTR Register

The DTR register allows the user to precisely adjust the offset of the data slicer input.

Register reset value = (20)

16

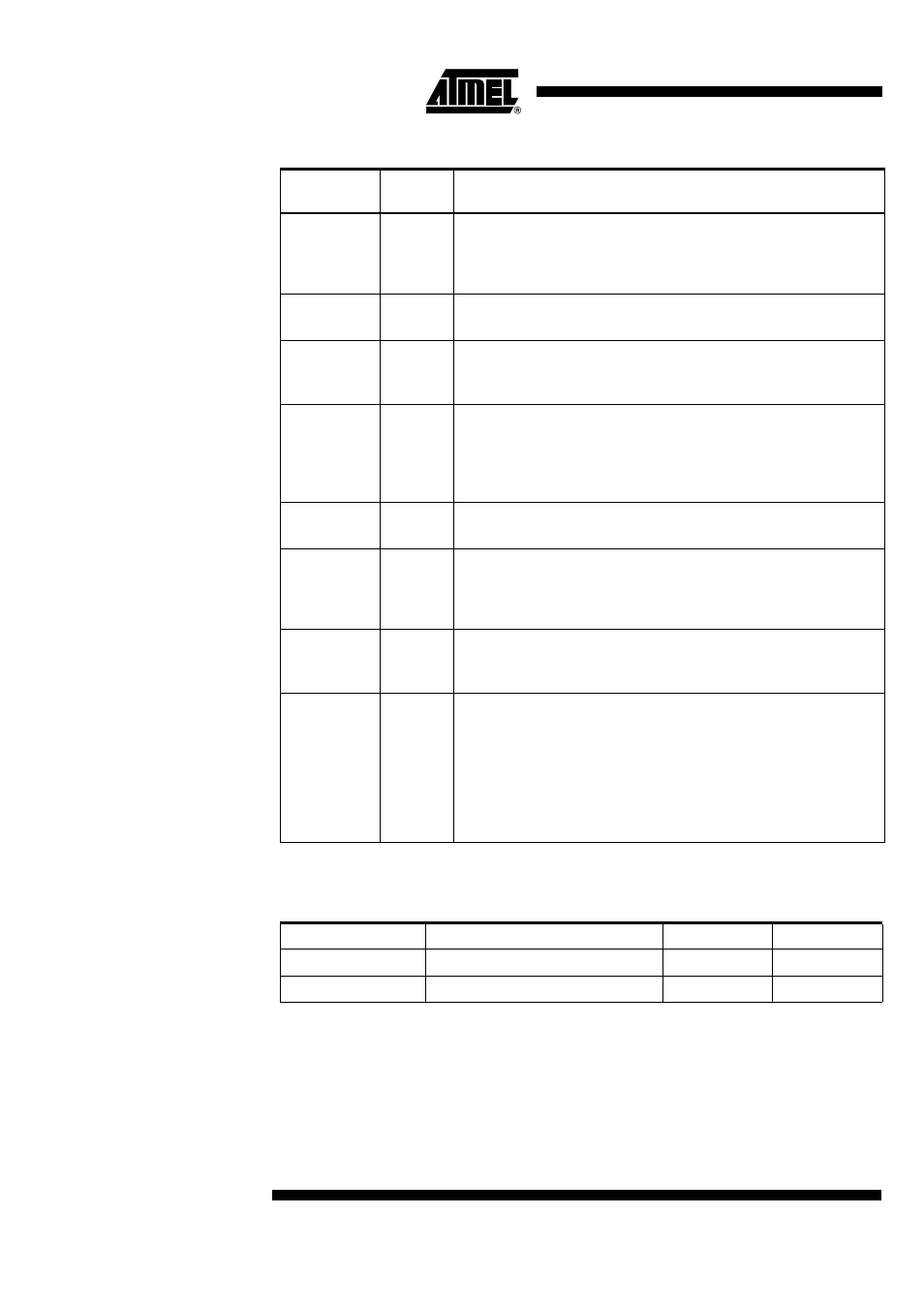

Table 11. Status Register Detailed Description

Name

Number

of bits

Comments

PLLL

1

PLL Lock flag

0: PLL unlocked

1: PLL locked

reset value: 0

MRSSI

6

Measured RSSI level

reset value: (00)

16

MVCC

6

Measured V

CC

power supply voltage or discriminator output when

MOFFSET = 1

reset value: (00)

16

WAKEUP

1

WAKEUP flag

Copy of the WAKEUP pin, but not affected by polarity selection.

0: no wake-up message received

1: wake-up message received

reset value: 0

-

1

Reserved

reset value: 0

MSGERR

1

Wake-up message error in test message mode

0: no error detected in the received message

1: message received with error

reset value: 0

MSGDATL

5

Wake-up message data length

length of the data stored in WUD (received message).

reset value: 0

MSGMRATE

10

Wake-up message measured data rate

bit period extracted from message header of the wake-up

message.

Measured as a multiple of 1.56 µs (like RATE in WUR register).

0: 1 x 1.56 µs

(vv)

10

: vv x 1.56 µs

(3ff)

16

: 1024 x 1.56 µs

reset value: (000)

16

Table 12. DTR Overview

Name

DSREF[3:0]

DISCHIGH

DISCLOW

nbit

5-2

1

0

init

(1000)

2

0

0