Figure 20: connecting an external load to dio pins – Rainbow Electronics 71M6542G User Manual

Page 60

60

© 2008–2011 Teridian Semiconductor Corporation

v1.1

Value in DIO_Rn[2:0]

Resource Selected for SEGDIOn or PB Pin

5

Low priority I/O interrupt (INT1)

Note:

Resources are selectable only on SEGDIO2 through SEGDIO11 and the

PB pin. See

(71M6541D/F) and

(71M6542F).

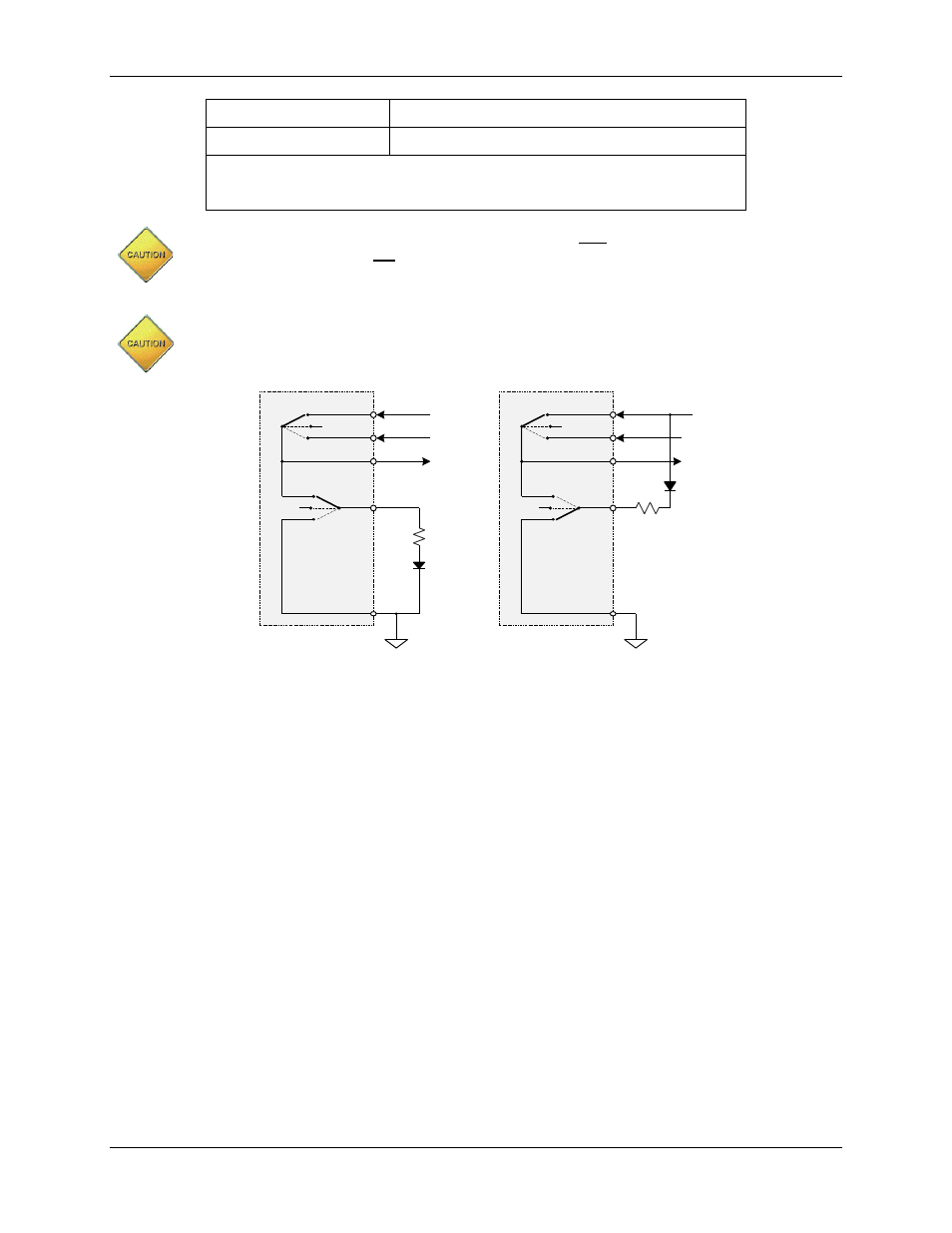

When driving LEDs, relay coils etc., the DIO pins should sink the current into GNDD (as

shown in

right), not source it from V3P3D (as shown in

, left). This is due

to the resistance of the internal switch that connects V3P3D to either V3P3SYS or VBAT. See

Sourcing current in or out of DIO pins other than those dedicated for wake functions, for

example with pull-up or pull-down resistors, must be avoided. Violating this rule leads to

increased quiescent current in sleep and LCD modes.

Figure 20: Connecting an External Load to DIO Pins

V3P3SYS

VBAT

V3P3D

DIO

GNDD

MISSION

BROWNOUT

LCD/SLEEP

LOW

HIGH

HIGH-Z

V3P3SYS

VBAT

V3P3D

DIO

GNDD

MISSION

BROWNOUT

LCD/SLEEP

LOW

HIGH

HIGH-Z

Not recommended

Recommended