Rainbow Electronics 71M6542G User Manual

Page 115

v1.1

© 2008–2011 Teridian Semiconductor Corporation

115

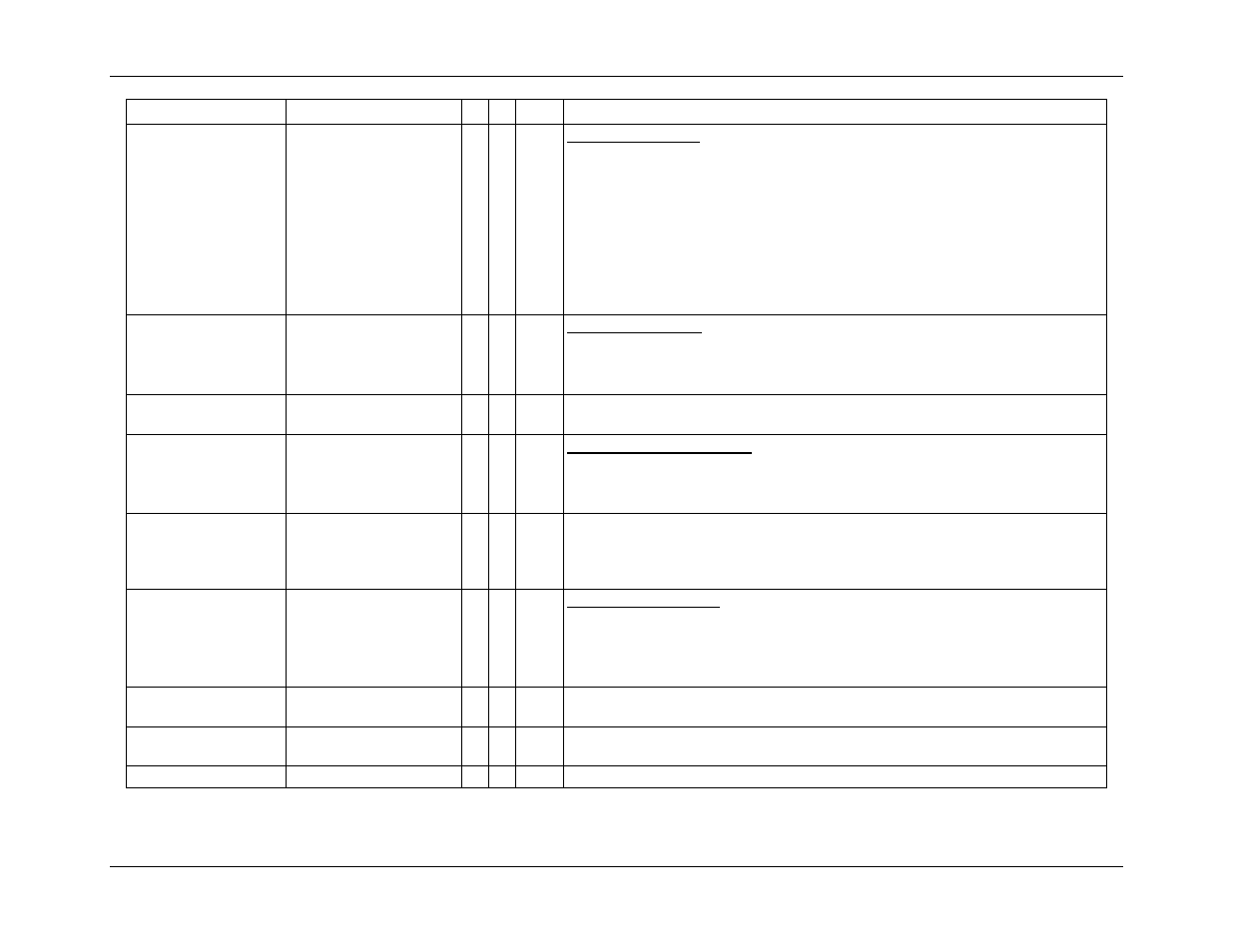

Name

Location

Rst Wk Dir Description

FLSH_ERASE[7:0]

SFR 94[7:0]

0 0

W

Flash Erase Initiate

FLSH_ERASE is used to initiate either the Flash Mass Erase cycle or the Flash

Page Erase cycle. Specific patterns are expected for FLSH_ERASE in order

to initiate the appropriate Erase cycle.

(default = 0x00).

0x55 = Initiate Flash Page Erase cycle. Must be proceeded by a write to

FLSH_PGADR[5:0] (SFR 0xB7[7:2]).

0xAA = Initiate Flash Mass Erase cycle. Must be proceeded by a write to

FLSH_MEEN and the ICE port must be enabled.

Any other pattern written to FLSH_ERASE has no effect.

FLSH_MEEN

SFR B2[1]

0 0

W

Mass Erase Enable

0 = Mass Erase disabled (default).

1 = Mass Erase enabled.

Must be re-written for each new Mass Erase cycle.

FLSH_PEND

SFR B2[3]

0 0

R

Indicates that a timed flash write is pending. If another flash write is attempted,

it is ignored.

FLSH_PGADR[5:0]

SFR B7[7:2]

0 0

W

Flash Page Erase Address

FLSH_PGADR[5:0] – Flash Page Address (page 0 thru 63) that is erased during

the Page Erase cycle. (default = 0x00).

Must be re-written for each new Page Erase cycle.

FLSH_PSTWR

SFR B2[2]

0 0 R/W

Enables timed flash writes. When 1, and if CE_E = 1, flash write requests are

stored in a one-element deep FIFO and are executed when CE_BUSY falls.

FLSH_PEND can be read to determine the status of the FIFO. If

FLSH_PSTWR = 0 or if CE_E = 0, flash writes are immediate.

FLSH_PWE

SFR B2[0]

0 0 R/W

Program Write Enable

0 = MOVX commands refer to External RAM Space, normal operation (default).

1 = MOVX @DPTR,A moves A to External Program Space (Flash) @ DPTR.

This bit is automatically reset after each byte written to flash. Writes to this bit

are inhibited when interrupts are enabled.

FLSH_RDE

2702[2]

– –

R

Indicates that the flash may be read by ICE or SPI slave. FLSH_RDE =

(!SECURE)

FLSH_UNLOCK[3:0]

2702[7:4]

0 0 R/W

Must be a ‘2’ to enable any flash modification. See the description of Flash

security for more details.

FLSH_WRE

2702[1]

– –

R

Indicates that the flash may be written through ICE or SPI slave ports.