6 timers and counters, Timers and counters, Table 22: pcon register bit description (sfr 0x87) – Rainbow Electronics 71M6542G User Manual

Page 39: Table 23: timers/counters mode description, Table 24: allowed timer/counter mode combinations, Table 21

v1.1

© 2008–2011 Teridian Semiconductor Corporation

39

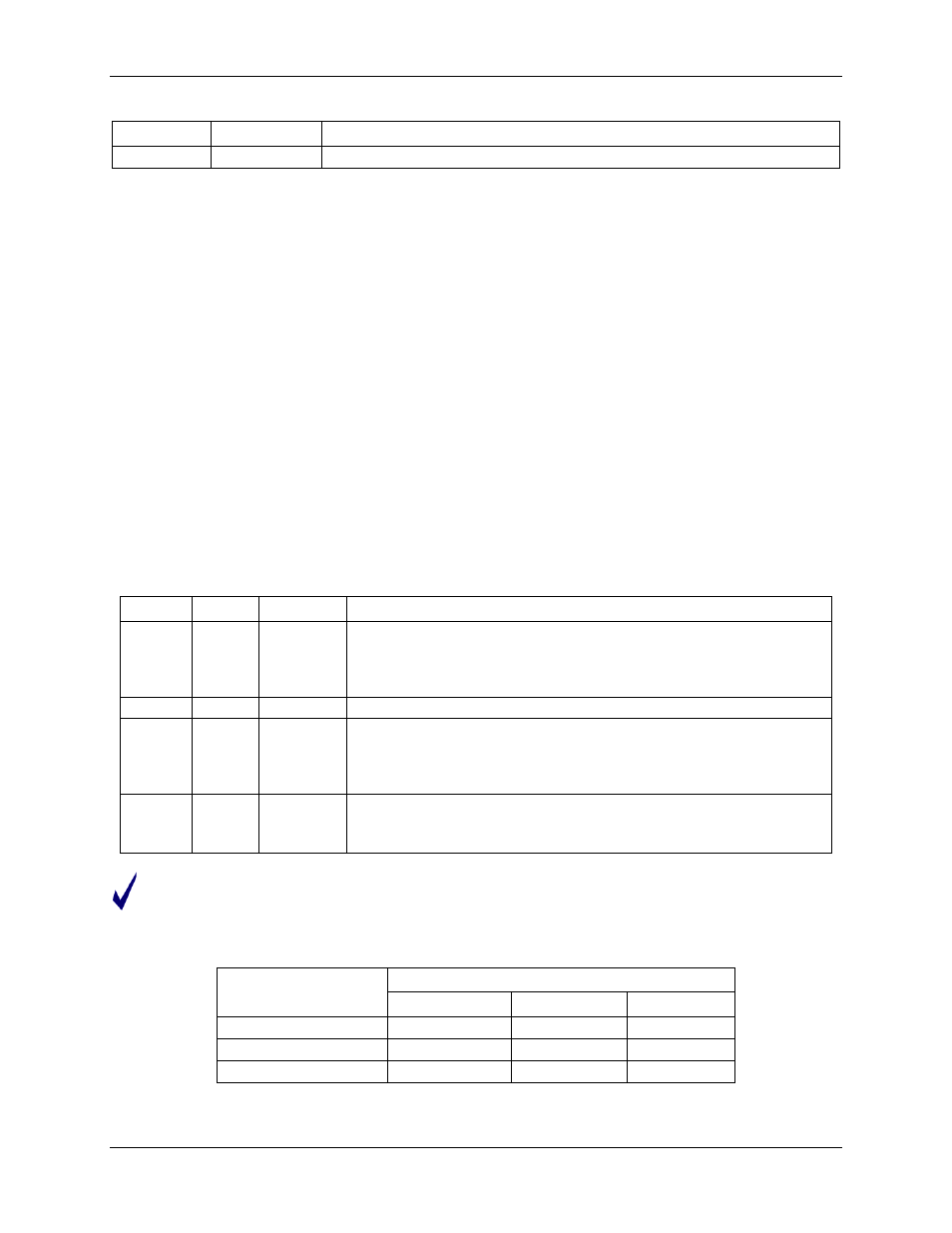

Table 21: PCON Register Bit Description (SFR 0x87)

Bit

Symbol

Function

PCON[7]

SMOD

The SMOD bit doubles the baud rate when set

2.4.6 Timers and Counters

The 80515 has two 16-bit timer/counter registers: Timer 0 and Timer 1. These registers can be configured

for counter or timer operations.

In timer mode, the register is incremented every machine cycle, i.e., it counts up once for every 12 periods

of the MPU clock. In counter mode, the register is incremented when the falling edge is observed at the

corresponding input signal T0 or T1 (T0 and T1 are the timer gating inputs derived from certain DIO pins,

see

). Since it takes 2 machine cycles to recognize a 1-to-0 event, the maximum input

count rate is 1/2 of the clock frequency (CKMPU). There are no restrictions on the duty cycle, however

to ensure proper recognition of the 0 or 1 state, an input should be stable for at least 1 machine cycle.

Four operating modes can be selected for Timer 0 and Timer 1, as shown in

. The

TMOD (SFR 0x89) Register, shown in

is used to select the appropriate mode. The timer/counter

operation is controlled by the TCON (SFR 0x88) Register, which is shown in

Bits TR1 (TCON[6])

and TR0 (TCON[4]) in the TCON register start their associated timers when set.

Table 22: Timers/Counters Mode Description

M1

M0

Mode

Function

0

0

Mode 0

13-bit Counter/Timer mode with 5 lower bits in the TL0 or TL1 (SFR

0x8A or SFR 0x8B) register and the remaining 8 bits in the TH0 or TH1

(SFR 0x8C or SFR 0x8D) register (for Timer 0 and Timer 1, respectively).

The 3 high order bits of TL0 and TL1 are held at zero.

0

1

Mode 1

16-bit Counter/Timer mode.

1

0

Mode 2

8-bit auto-reload Counter/Timer. The reload value is kept in TH0 or

TH1, while TL0 or TL1 is incremented every machine cycle. When

TL(x) overflows, a value from TH(x) is copied to TL(x) (where x is 0

for counter/timer 0 or 1 for counter/timer 1.

1

1

Mode 3

If Timer 1 M1 and M0 bits are set to 1, Timer 1 stops.

If Timer 0 M1 and M0 bits are set to 1, Timer 0 acts as two independent

8-bit Timer/Counters.

In Mode 3, TL0 is affected by TR0 and gate control bits, and sets the TF0 flag on overflow, while TH0

is affected by the TR1 bit, and the TF1 flag is set on overflow.

specifies the combinations of operation modes allowed for Timer 0 and Timer 1.

Table 23: Allowed Timer/Counter Mode Combinations

Timer 1

Mode 0

Mode 1

Mode 2

Timer 0 - mode 0

Yes

Yes

Yes

Timer 0 - mode 1

Yes

Yes

Yes

Timer 0 - mode 2

Not allowed

Not allowed

Yes