Preliminary – Rainbow Electronics T89C51CC02 User Manual

Page 87

Rev.A - May 17, 2001

87

Preliminary

T89C51CC02

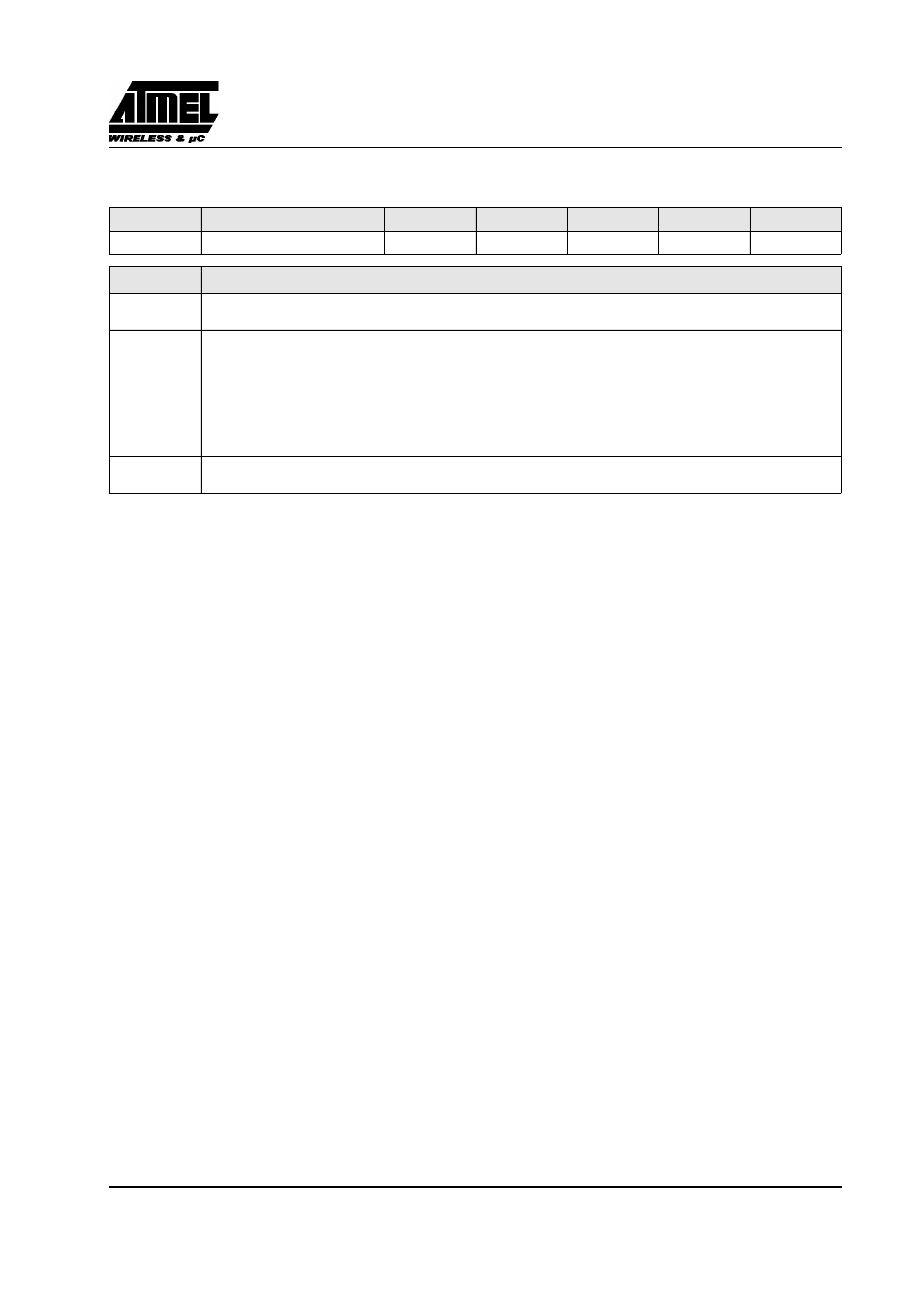

CANBT1 (S:B4h)

CAN Bit Timing Registers 1

Note:

The CAN controller bit timing registers must be accessed only if the CAN controller is disabled with the ENA bit of the CANGCON register set to 0.

See Figure 60.

No default value after reset.

Figure 74. CANBT1 Register

7

6

5

4

3

2

1

0

-

BRP 5

BRP 4

BRP 3

BRP 2

BRP 1

BRP 0

-

Bit Number Bit Mnemonic

Description

7

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

6-1

BRP5:0

Baud rate prescaler

The period of the CAN controller system clock Tscl is programmable and determines the individual

bit timing.

0

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Tscl

BRP 5

…

0

[

]

1

+

Fcan

---------------------------------------

=

See also other documents in the category Rainbow Electronics Sensors:

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)