flash parallel programming, Preliminary – Rainbow Electronics T89C51CC02 User Manual

Page 37

Rev.A - May 17, 2001

37

Preliminary

T89C51CC02

10.2.1. Flash Parallel Programming

The three lock bits in Hardware byte are programmed according to Table, will provide different level of protection

for the on-chip code and data located in FM0 and FM1.

The only way for write this bits are the parallel mode.

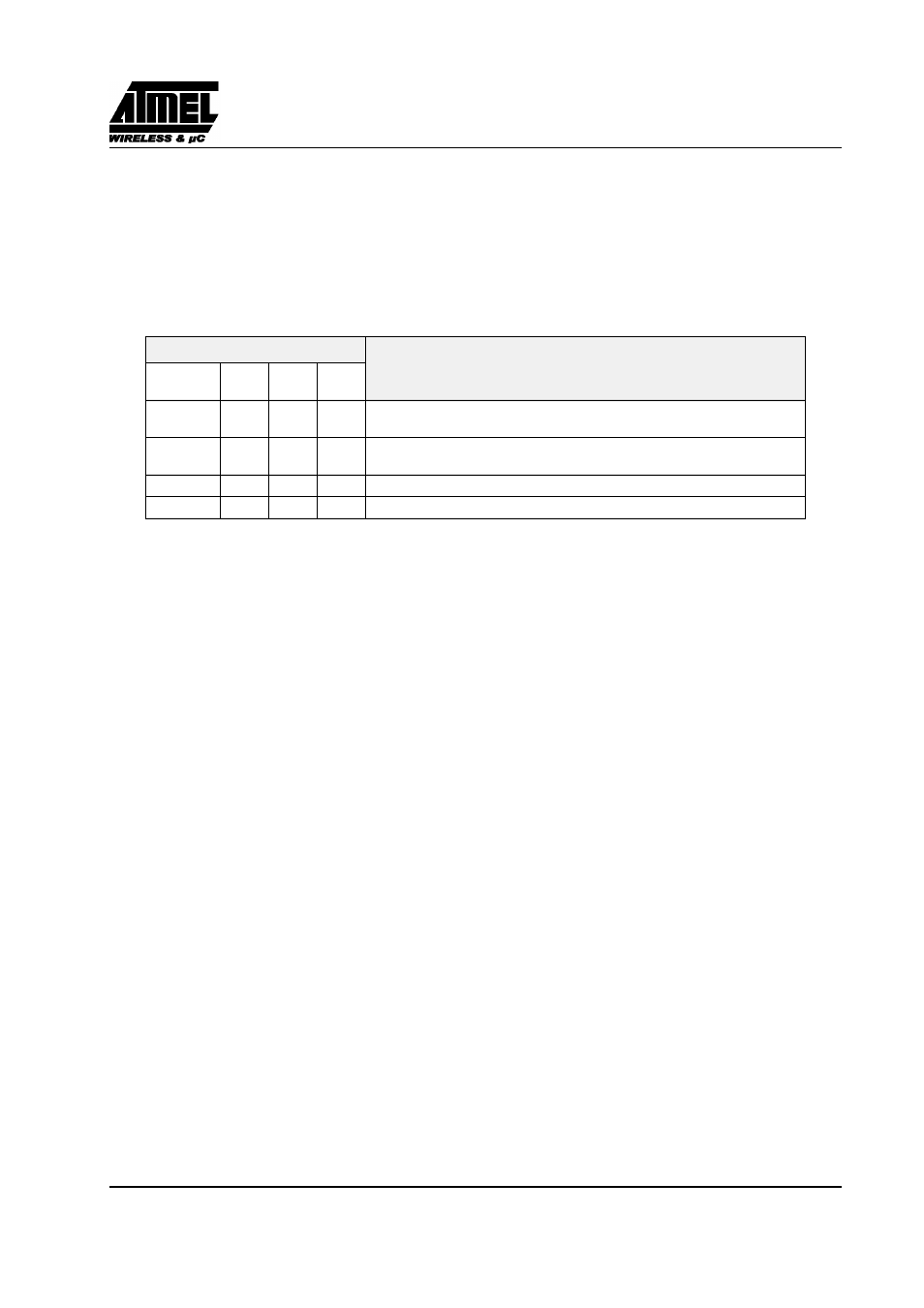

Table 16. Program Lock bit

Program Lock bits

U: unprogrammed

P: programmed

WARNING: Security level 2 and 3 should only be programmed after Flash and Core verification.

Program Lock bits

These security bits protect the code access through the parallel programming interface. They are set by default to

level 4.

Program Lock Bits

Protection description

Security

level

LB0

LB1

LB2

1

U

U

U

No program lock features enabled. MOVC instruction executed from external program

memory returns non encrypted data.

2

P

U

U

MOVC instruction executed from external program memory are disabled from fetching

code bytes from internal memory.

3

U

P

U

Same as 2, also verify through parallel programming interface is disabled.

4

U

U

P

Same as 3, also external execution is disabled.