dual data pointer, description, application – Rainbow Electronics T89C51CC02 User Manual

Page 30: Preliminary, Dual data pointer

30

Rev.A - May 17, 2001

Preliminary

T89C51CC02

8.3. Dual Data Pointer

8.3.1. Description

The T89C51CC02 implements a second data pointer for speeding up code execution and reducing code size in

case of intensive usage of external memory accesses.

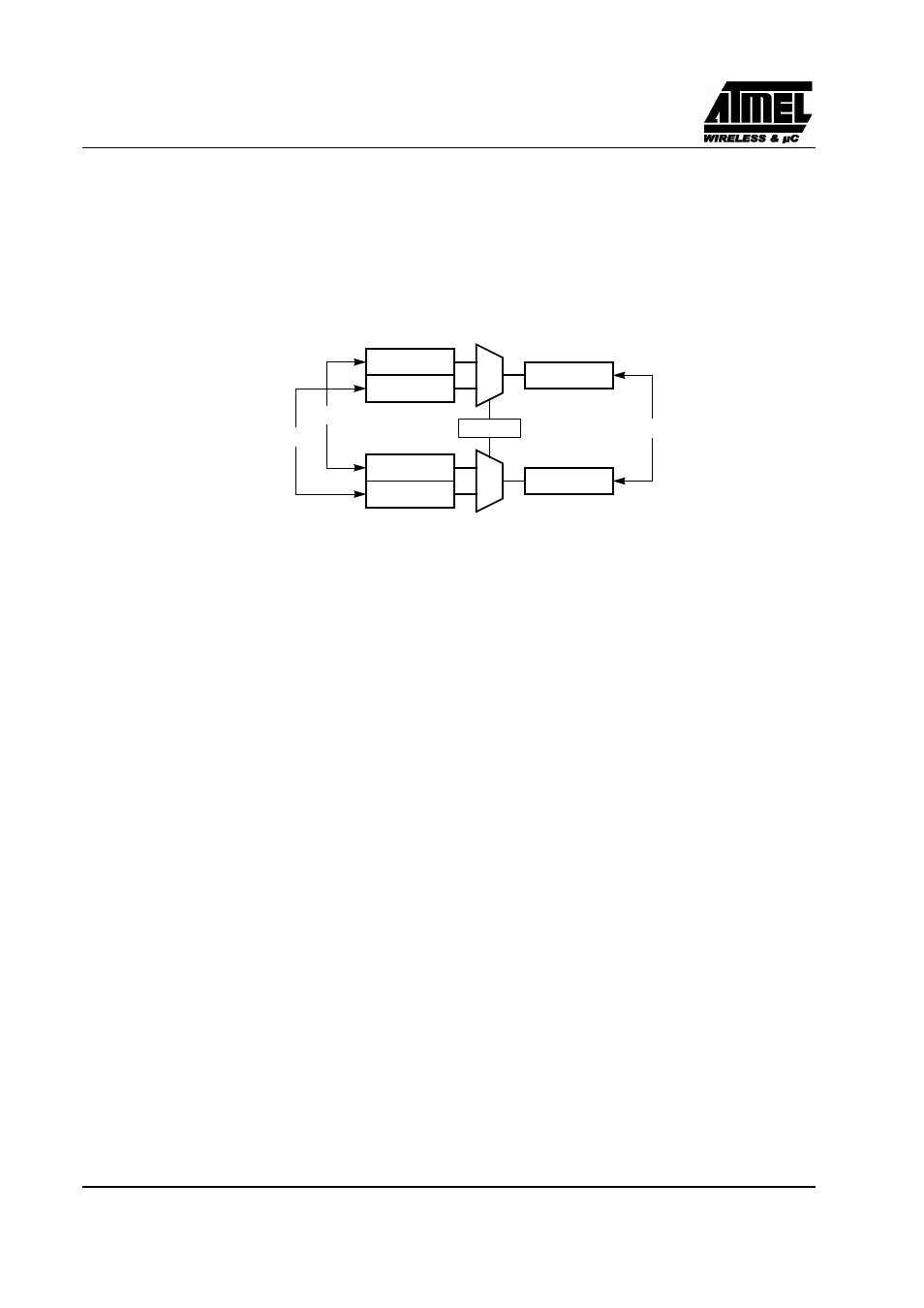

DPTR0 and DPTR1 are seen by the CPU as DPTR and are accessed using the SFR addresses 83h and 84h that

are the DPH and DPL addresses. The DPS bit in AUXR1 register (see Figure 17) is used to select whether DPTR

is the data pointer 0 or the data pointer 1 (see Figure 15).

Figure 15. Dual Data Pointer Implementation

8.3.2. Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for

example, block operations (copy, compare, search …) are well served by using one data pointer as a “source”

pointer and the other one as a “destination” pointer.

Hereafter is an example of block move implementation using the two pointers and coded in assembler. Latest C

compiler take also advantage of this feature by providing enhanced algorithm libraries.

The INC instruction is a short (2 bytes) and fast (6 CPU clocks) way to manipulate the DPS bit in the AUXR1

register. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply

toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper

sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0'

or '1' on entry.

; ASCII

block

move

using

dual

data

pointers

; Modifies

DPTR0,

DPTR1,

A

and

PSW

; Ends

when

encountering

NULL

character

; Note:

DPS

exits

opposite

of

entry

state

unless

an

extra

INC

AUXR1

is

added

AUXR1

EQU

0A2h

move:

mov

DPTR,#SOURCE

; address

of

SOURCE

inc

AUXR1

; switch

data

pointers

mov

DPTR,#DEST

; address

of

DEST

mv_loop:

inc

AUXR1

; switch

data

pointers

movx

A,@DPTR

; get

a

byte

from

SOURCE

inc

DPTR

; increment

SOURCE

address

inc

AUXR1

; switch

data

pointers

movx

@DPTR,A

; write

the

byte

to

DEST

inc

DPTR

; increment

DEST

address

jnz

mv_loop

; check

for

NULL

terminator

end_move:

0

1

DPH0

DPH1

DPL0

0

1

DPS

AUXR1.0

DPH

DPL

DPL1

DPTR

DPTR0

DPTR1