watchdog timer, introduction, Preliminary – Rainbow Electronics T89C51CC02 User Manual

Page 64: Watchdog timer, Introduction

64

Rev.A - May 17, 2001

Preliminary

T89C51CC02

14. WatchDog Timer

14.1. Introduction

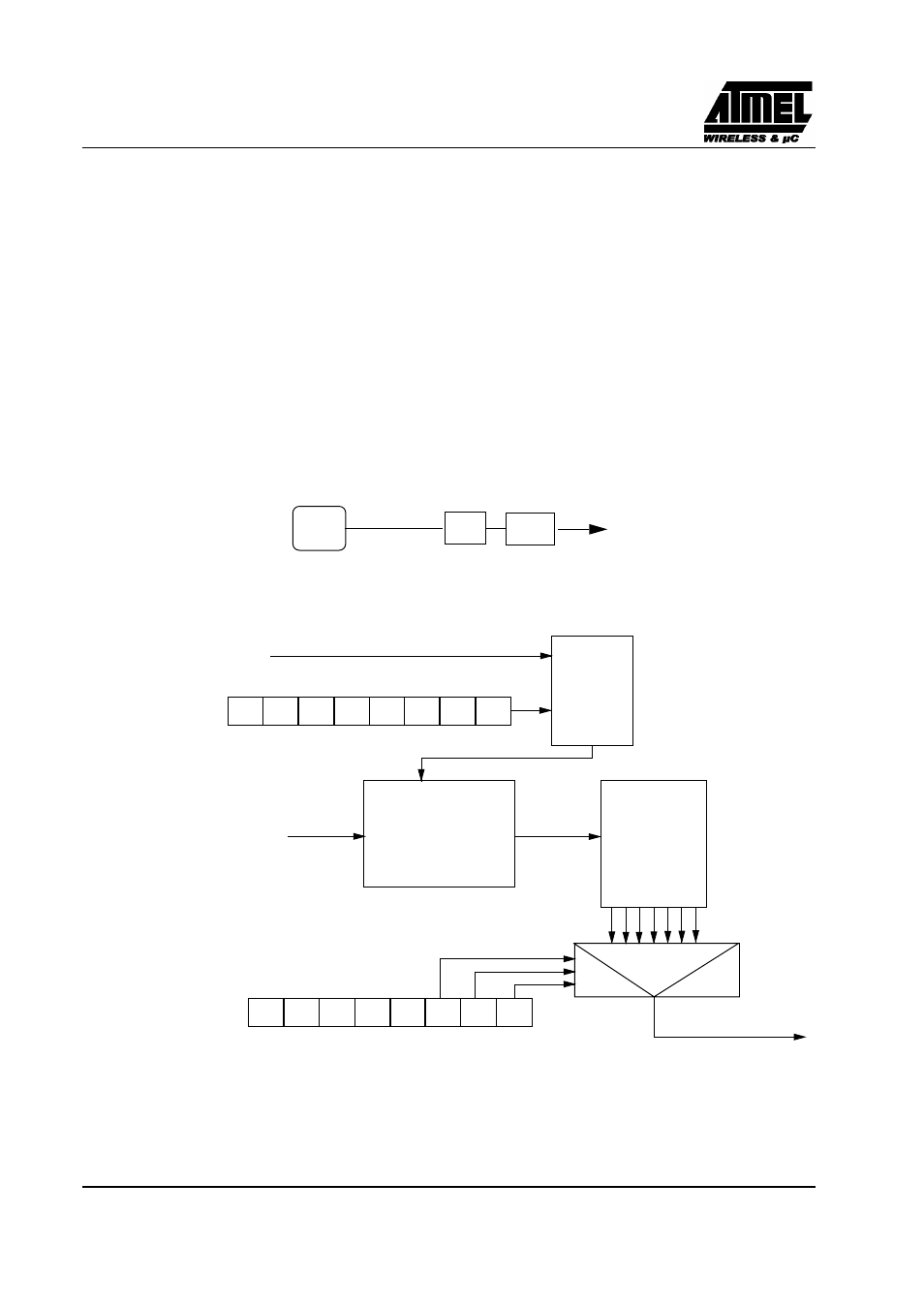

T89C51CC02 contains a powerful programmable hardware WatchDog Timer (WDT) that automatically resets the

chip if it software fails to reset the WDT before the selected time interval has elapsed. It permits large Time-Out

ranking from 16ms to 2s @Fosc = 12MHz.

This WDT consist of a 14-bit counter plus a 7-bit programmable counter, a WatchDog Timer reset register

(WDTRST) and a WatchDog Timer programming (WDTPRG) register. When exiting reset, the WDT is -by default-

disable. To enable the WDT, the user has to write the sequence 1EH and E1H into WDRST register. When the

WatchDog Timer is enabled, it will increment every machine cycle while the oscillator is running and there is no

way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows,

it will generate an output RESET pulse at the RST pin. The RESET pulse duration is 96xT

OSC

, where T

OSC

=1/

F

OSC

. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be

executed within the time required to prevent a WDT reset.

Figure 53. WatchDog Timer

ч

6

ч

PS

CPU and Peripheral

Clock

Fwd

CLOCK

RESET

Decoder

Control

WDTRST

WR

Enable

14-bit COUNTER

7-bit COUNTER

Outputs

PERIPHERAL CLOCK

RESET

-

-

-

-

-

2

1

0