Special function io register – sfior, Table 25, Atmega8515(l) – Rainbow Electronics ATmega8515L User Manual

Page 62

62

ATmega8515(L)

2512A–AVR–04/02

The following subsections shortly describe the alternate functions for each port, and

relate the overriding signals to the alternate function. Refer to the alternate function

description for further details.

Special Function IO Register –

SFIOR

• Bit 2 – PUD: Pull-up Disable

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn

and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01).

See “Configuring the Pin” on page 57 for more details about this feature.

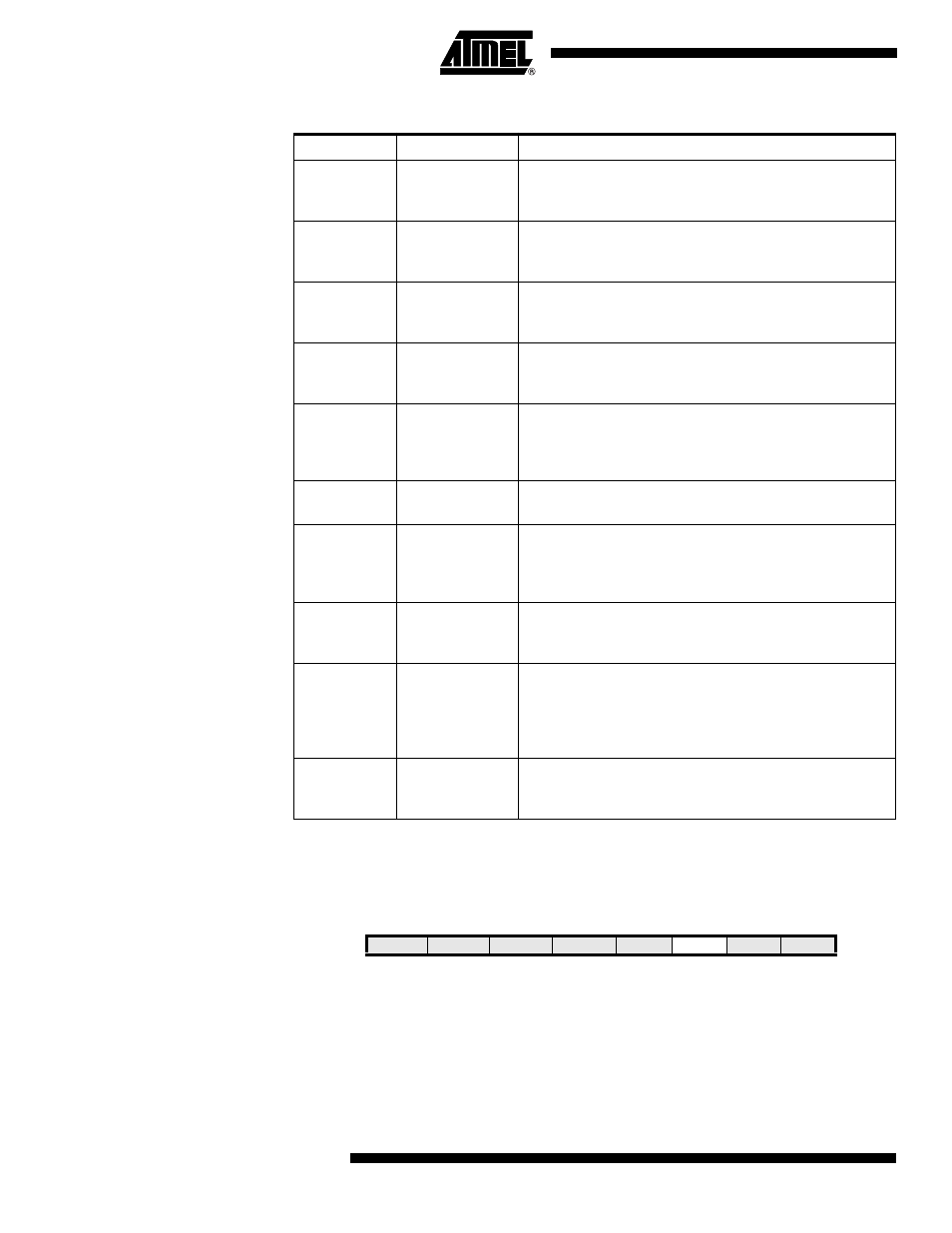

Table 25. Generic Description of Overriding Signals for Alternate Functions.

Signal Name

Full Name

Description

PUOE

Pull-up Override

Enable

If this signal is set, the pull-up enable is controlled by the

PUOV signal. If this signal is cleared, the pull-up is

enabled when {DDxn, PORTxn, PUD} = 0b010.

PUOV

Pull-up Override

Value

If PUOE is set, the pull-up is enabled/disabled when

PUOV is set/cleared, regardless of the setting of the

DDxn, PORTxn, and PUD Register bits.

DDOE

Data Direction

Override Enable

If this signal is set, the Output Driver Enable is controlled

by the DDOV signal. If this signal is cleared, the Output

driver is enabled by the DDxn Register bit.

DDOV

Data Direction

Override Value

If DDOE is set, the Output Driver is enabled/disabled

when DDOV is set/cleared, regardless of the setting of the

DDxn Register bit.

PVOE

Port Value

Override Enable

If this signal is set and the Output Driver is enabled, the

port value is controlled by the PVOV signal. If PVOE is

cleared, and the Output Driver is enabled, the port Value is

controlled by the PORTxn Register bit.

PVOV

Port Value

Override Value

If PVOE is set, the port value is set to PVOV, regardless of

the setting of the PORTxn Register bit.

DIEOE

Digital Input

Enable Override

Enable

If this bit is set, the Digital Input Enable is controlled by the

DIEOV signal. If this signal is cleared, the Digital Input

Enable is determined by MCU-state (Normal mode, sleep

modes).

DIEOV

Digital Input

Enable Override

Value

If DIEOE is set, the Digital Input is enabled/disabled when

DIEOV is set/cleared, regardless of the MCU state

(Normal mode, sleep modes).

DI

Digital Input

This is the Digital Input to alternate functions. In the figure,

the signal is connected to the output of the schmitt trigger

but before the synchronizer. Unless the Digital Input is

used as a clock source, the module with the alternate

function will use its own synchronizer.

AIO

Analog

Input/output

This is the Analog Input/Output to/from alternate functions.

The signal is connected directly to the pad, and can be

used bi-directionally.

Bit

7

6

5

4

3

2

1

0

–

XMBK

XMM2

XMM1

XMM0

PUD

–

PSR10

SFIOR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0