Phase and frequency correct pwm mode, Atmega8515(l) – Rainbow Electronics ATmega8515L User Manual

Page 112

112

ATmega8515(L)

2512A–AVR–04/02

Phase and Frequency Correct

PWM Mode

The

phase and frequency correct Pulse Width Modulation, or phase and frequency cor-

rect PWM mode (WGM13:0 = 8 or 9) provides a high resolution phase and frequency

correct PWM waveform generation option. The phase and frequency correct PWM

mode is, like the phase correct PWM mode, based on a dual-slope operation. The

counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOT-

TOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared

on the compare match between TCNT1 and OCR1x while upcounting, and set on the

compare match while downcounting. In inverting Compare Output mode, the operation

is inverted. The dual-slope operation gives a lower maximum operation frequency com-

pared to the single-slope operation. However, due to the symmetric feature of the dual-

slope PWM modes, these modes are preferred for motor control applications.

The main difference between the phase correct, and the phase and frequency correct

PWM mode is the time the OCR1x Register is updated by the OCR1x Buffer Register,

(see Figure 53 and Figure 54).

The PWM resolution for the phase and frequency correct PWM mode can be defined by

either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to

0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM

resolution in bits can be calculated using the following equation:

In phase and frequency correct PWM mode the counter is incremented until the counter

value matches either the value in ICR1 (WGM13:0 = 8), or the value in OCR1A

(WGM13:0 = 9). The counter has then reached the TOP and changes the count direc-

tion. The TCNT1 value will be equal to TOP for one timer clock cycle. The timing

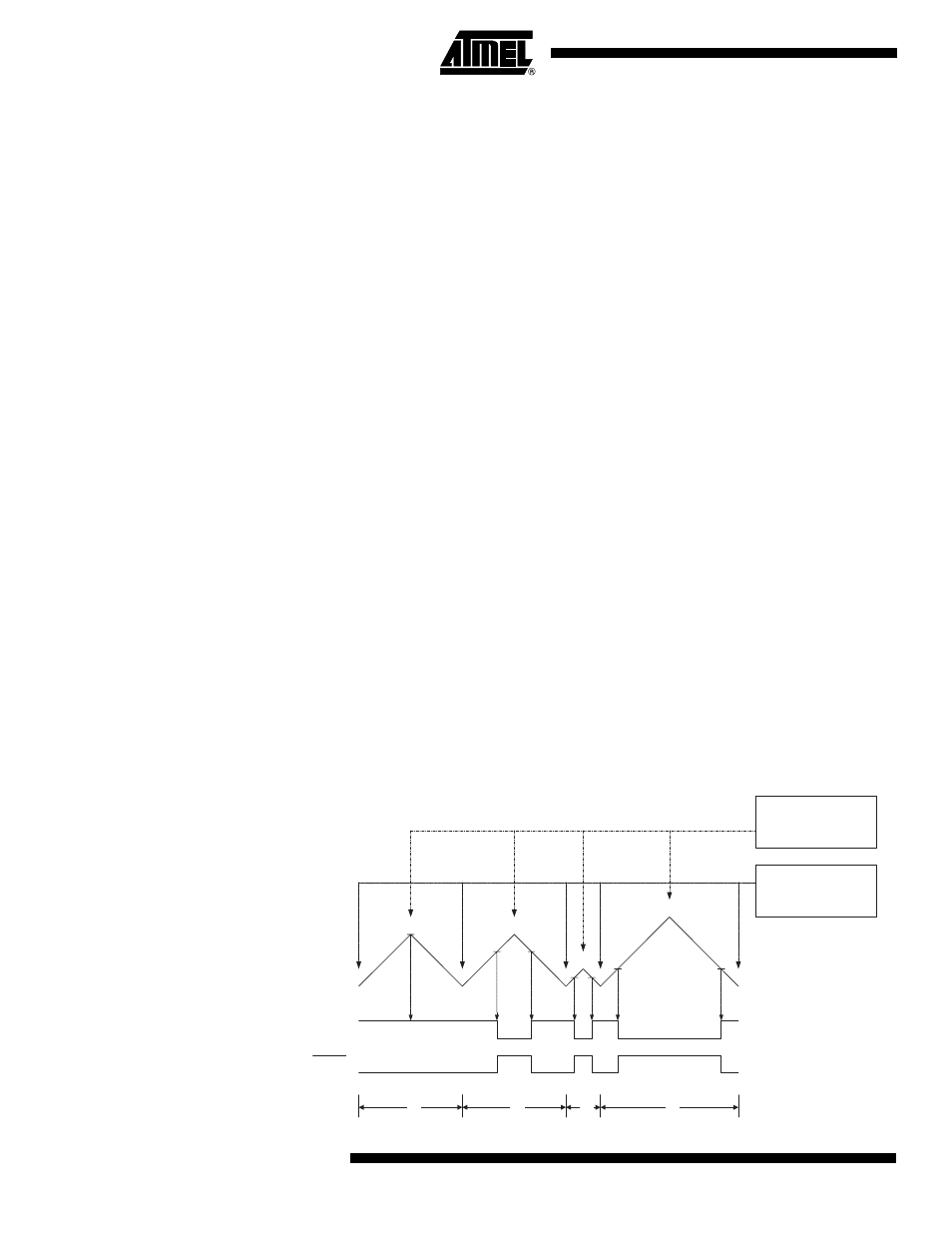

diagram for the phase correct and frequency correct PWM mode is shown on Figure 54.

The figure shows phase and frequency correct PWM mode when OCR1A or ICR1 is

used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for

illustrating the dual-slope operation. The diagram includes non-inverted and inverted

PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare

matches between OCR1x and TCNT1. The OC1x interrupt flag will be set when a com-

pare match occurs.

Figure 54. Phase and Frequency Correct PWM Mode, Timing Diagram

R

PFCPW M

TOP

1

+

(

)

log

2

( )

log

-----------------------------------

=

OCRnx/TOP Update and

TOVn Interrupt Flag Set

(Interrupt on Bottom)

OCnA Interrupt Flag Set

or ICFn Interrupt Flag Set

(Interrupt on TOP)

1

2

3

4

TCNTn

Period

OCnx

OCnx

(COMnx1:0 = 2)

(COMnx1:0 = 3)