Usart control and status register a – ucsra, Atmega8515(l) – Rainbow Electronics ATmega8515L User Manual

Page 151

151

ATmega8515(L)

2512A–AVR–04/02

The transmit buffer can only be written when the UDRE flag in the UCSRA Register is

set. Data written to UDR when the UDRE flag is not set, will be ignored by the USART

Transmitter. When data is written to the transmit buffer, and the Transmitter is enabled,

the Transmitter will load the data into the Transmit Shift Register when the Shift Register

is empty. Then the data will be serially transmitted on the TxD pin.

The receive buffer consists of a two level FIFO. The FIFO will change its state whenever

the receive buffer is accessed. Due to this behavior of the receive buffer, do not use

read modify write instructions (SBI and CBI) on this location. Be careful when using bit

test instructions (SBIC and SBIS), since these also will change the state of the FIFO.

USART Control and Status

Register A – UCSRA

• Bit 7 – RXC: USART Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when the

receive buffer is empty (i.e., does not contain any unread data). If the receiver is dis-

abled, the receive buffer will be flushed and consequently the RXC bit will become zero.

The RXC flag can be used to generate a Receive Complete interrupt (see description of

the RXCIE bit).

• Bit 6 – TXC: USART Transmit Complete

This flag bit is set when the entire frame in the Transmit Shift Register has been shifted

out and there are no new data currently present in the transmit buffer (UDR). The TXC

flag bit is automatically cleared when a transmit complete interrupt is executed, or it can

be cleared by writing a one to its bit location. The TXC flag can generate a Transmit

Complete interrupt (see description of the TXCIE bit).

• Bit 5 – UDRE: USART Data Register Empty

The UDRE flag indicates if the transmit buffer (UDR) is ready to receive new data. If

UDRE is one, the buffer is empty, and therefore ready to be written. The UDRE flag can

generate a Data Register Empty interrupt (see description of the UDRIE bit).

UDRE is set after a reset to indicate that the Transmitter is ready.

• Bit 4 – FE: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when

received. For example, when the first stop bit of the next character in the receive buffer

is zero. This bit is valid until the receive buffer (UDR) is read. The FE bit is zero when

the stop bit of received data is one. Always set this bit to zero when writing to UCSRA.

• Bit 3 – DOR: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the

receive buffer is full (two characters), it is a new character waiting in the Receive Shift

Register, and a new start bit is detected. This bit is valid until the receive buffer (UDR) is

read. Always set this bit to zero when writing to UCSRA.

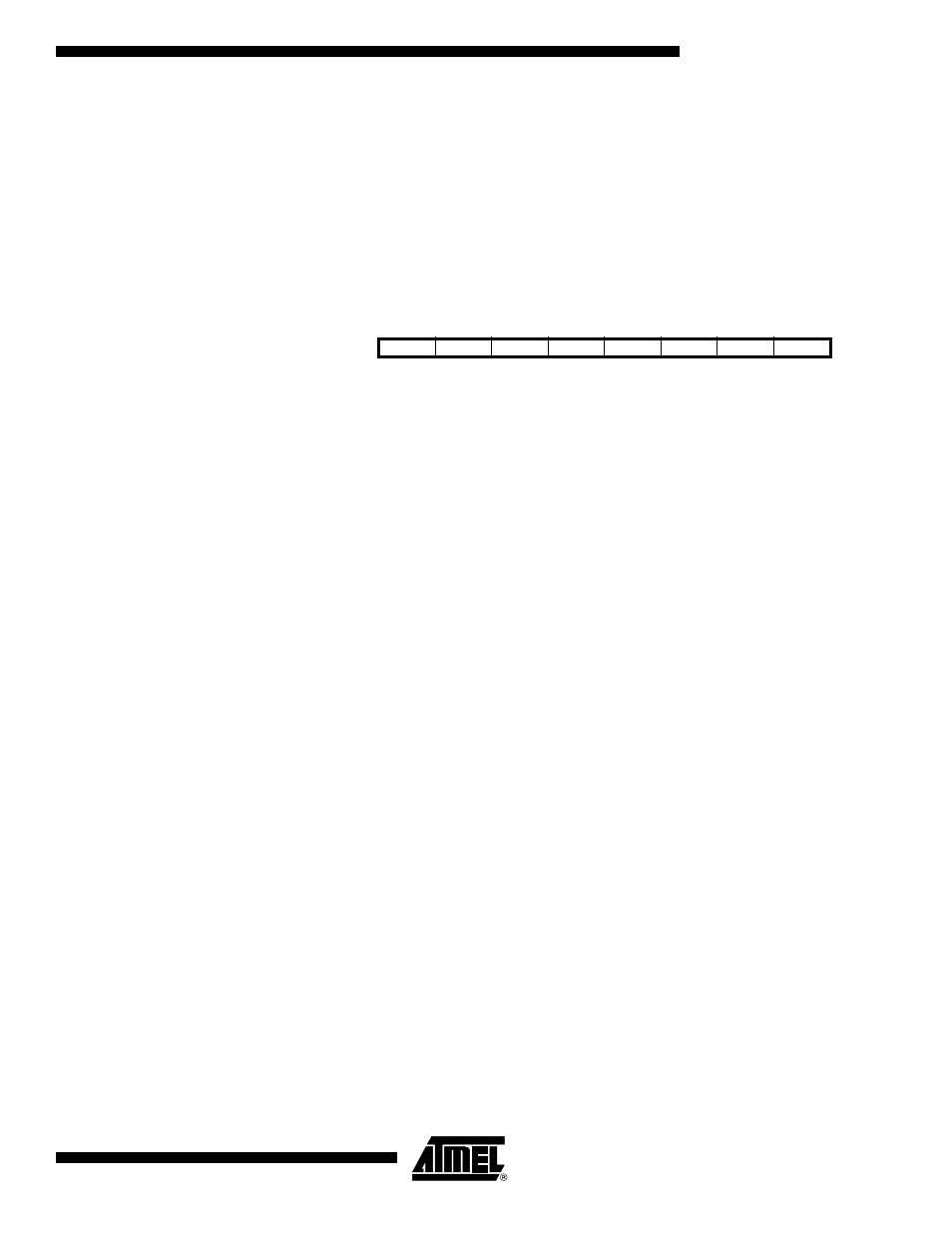

Bit

7

6

5

4

3

2

1

0

RXC

TXC

UDRE

FE

DOR

PE

U2X

MPCM

UCSRA

Read/Write

R

R/W

R

R

R

R

R/W

R/W

Initial Value

0

0

1

0

0

0

0

0