Data memory access times, Atmega8515(l) – Rainbow Electronics ATmega8515L User Manual

Page 16

16

ATmega8515(L)

2512A–AVR–04/02

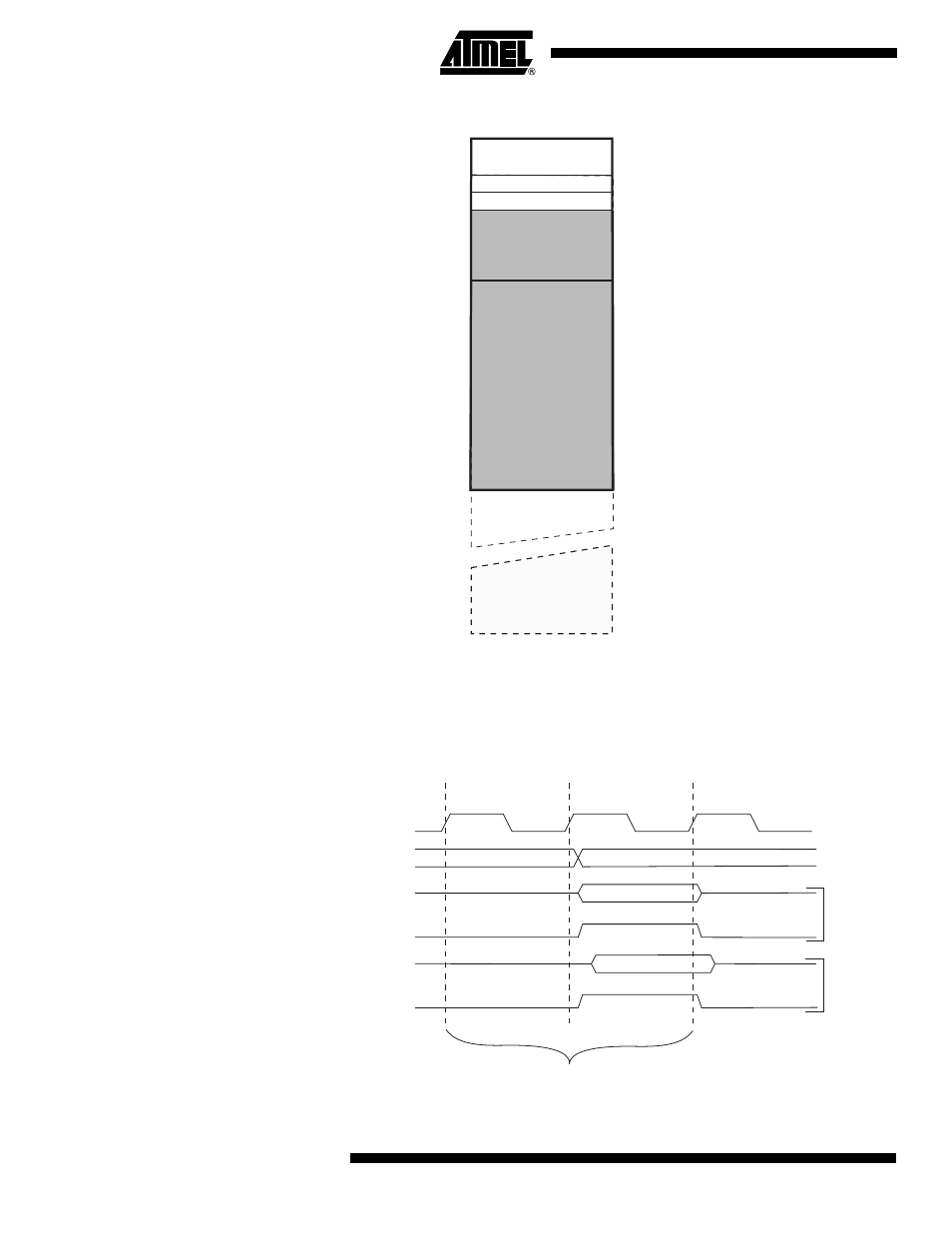

Figure 9. Data Memory Map

Data Memory Access Times

This section describes the general access timing concepts for internal memory access.

The internal data SRAM access is performed in two clk

CPU

cycles as described in Figure

Figure 10. On-chip Data SRAM Access Cycles

32 Registers

64 I/O Registers

Internal SRAM

(512 x 8)

$0000 - $001F

$0020 - $005F

$0260

$025F

$FFFF

$0060

Data Memory

External SRAM

(0 - 64K x 8)

clk

WR

RD

Data

Data

Address

Address Valid

T1

T2

T3

Compute Address

Read

Wr

ite

CPU

Memory Access Instruction

Next Instruction

See also other documents in the category Rainbow Electronics Sensors:

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)