4 lookup table entry format, Lookup table entry format, Upstream lookup table address translation – Intel 21555 User Manual

Page 40: Figure 8

40

21555 Non-Transparent PCI-to-PCI Bridge User Manual

Address Decoding

Note:

The indirect access mechanism must be used only by one interface at a time. When access to the

lookup table by multiple masters is possible, it is strongly recommended that the Generic Own bits

or some other semaphore mechanism be used to restrict access to one master at a time.

The 21555 conditionally asserts s_inta_l when an upstream memory transaction transfers data addressing the last

Dword in a page. This interrupt alerts the local processor that the page entry may need updating. The 21555

implements an event bit and interrupt mask bit for each of the 64 pages (entries) in the upstream window.

Note:

The page entry of the lookup table should not be updated while the initiator is still performing

transactions addressing that page.

4.3.4

Lookup Table Entry Format

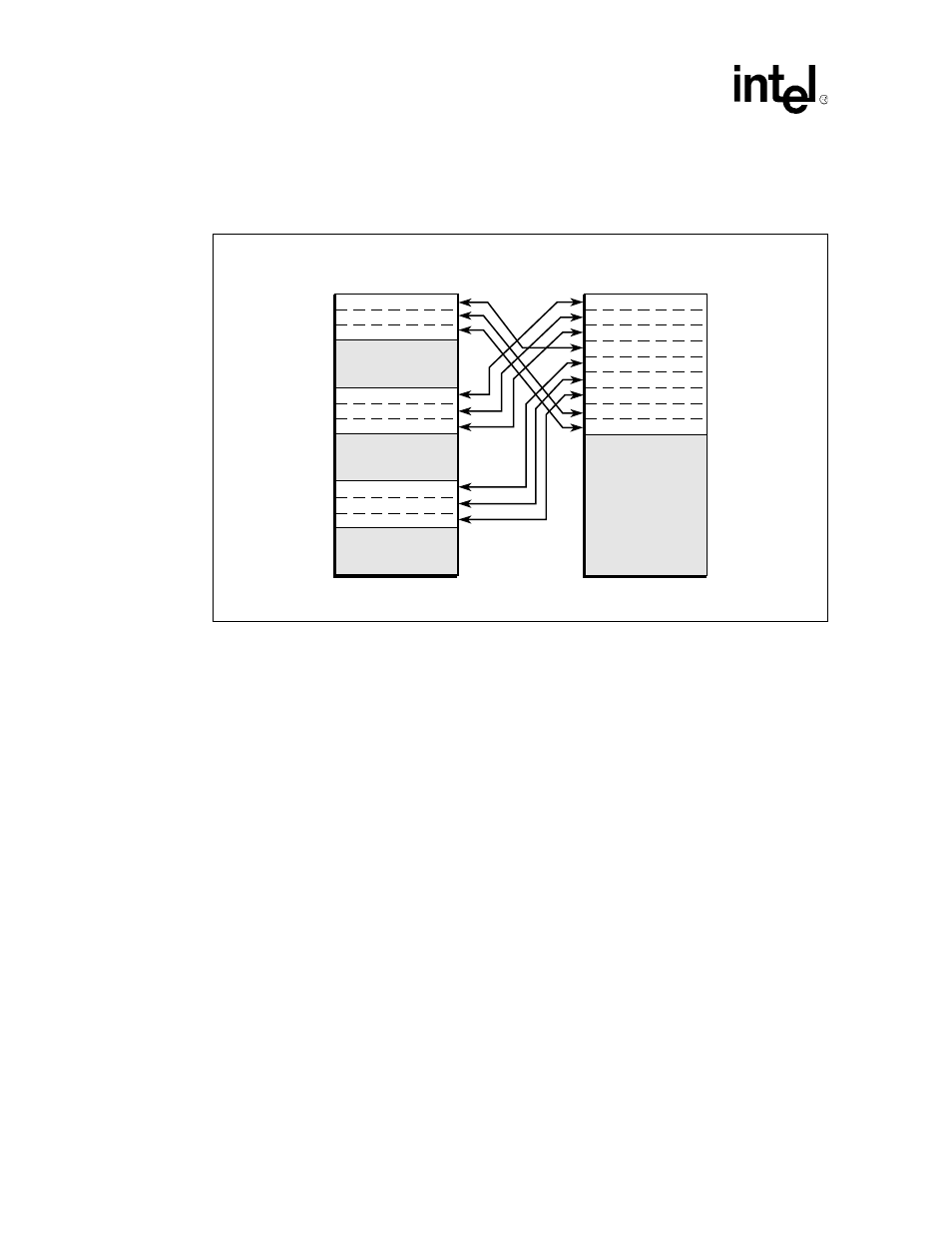

shows the format for an entry in the lookup table. The number of bits of the entry used for the new

translated base address is variable and is listed in

. The maximum number of bits used are bits [31:8],

corresponding to a 256-byte page size, while the minimum number of bits used is bit [31], corresponding to a 32

Mbyte page size. The next 4 to 27 bits, depending on the number of bits used for the base address, are reserved. The

low 4 bits are used for control. Two control bits are defined, one indicating whether the entry is a valid entry, and

one indicating whether prefetchable behavior should be used on memory reads. When the entry is not valid, the

21555 treats the transaction addressing that page as if a master abort were detected on the target interface.

For writes, the 21555 discards memory write data and asserts s_serr_l, when the SERR# Disable for Master Abort

during Posted Write bit is 0. For reads, the 21555 returns FFFFFFFFh on reads if the Master Abort Mode bit is 0, or

returns a target abort if the Master Abort Mode bit is a 1.

Figure 8. Upstream Lookup Table Address Translation

A7466-01

Base + Offset

Translated

Base + Offset

Primary Address Map

Secondary Address Map