Intel 21555 User Manual

Page 125

21555 Non-Transparent PCI-to-PCI Bridge User Manual

125

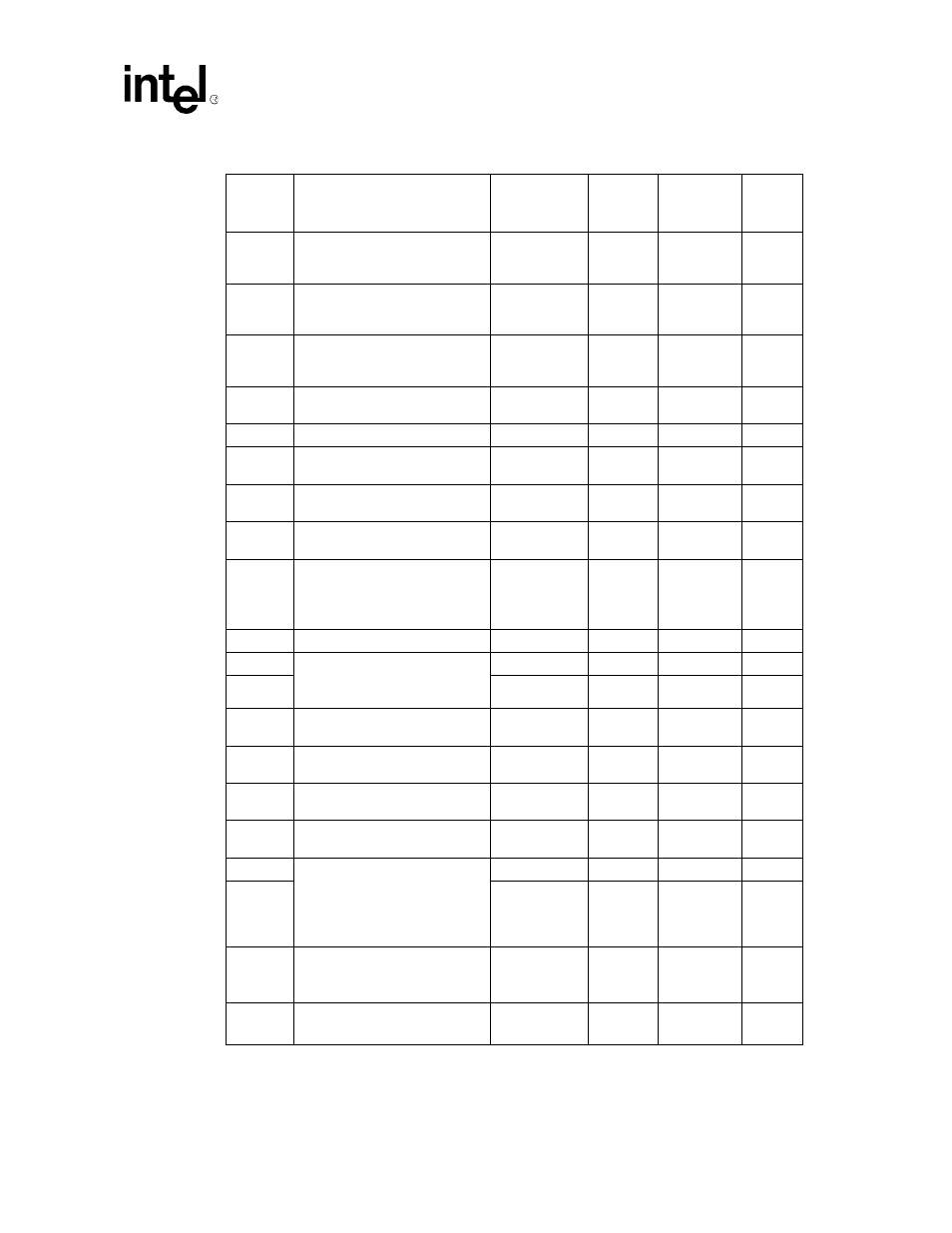

List of Registers

C7:C4

Downstream I/O or Memory 1

and Upstream I/O or Memory 0

Setup Registers, page 138

00000000

Y

Secondary

Y

CB:C8

Downstream Memory 0, 2, 3, and

Upstream Memory 1 Setup

Registers, page 139

00000000

Y

Secondary

Y

CD:CC

Chip Control 0 Register, page

156

0y00

y = 0 or 4

(Strapped)

Y

[15:11, 9:0]Y

[10]

secondary

Y

CF:CE

Chip Control 1 Register, page

160

0000

Y

Y

Y

D1:D0

Chip Status Register, page 162

0000

—

W1TC

Y

D3:D2

Arbiter Control Register, page

183

0200

Y

Y

Y

D4

Primary SERR# Disable

Register, page 184

00

Y

Y

Y

D5

Secondary SERR# Disable

Register, page 184

00

Y

Y

Y

D7:D6

Mode Setting Configuration

Register, page 179

Determined by Parallel ROM

Strapping Options

0000

—

N

Y

DB:D8

Reset Control Register, page 188

0000

—

Primary

Y

DC

Power Management ECP ID and

Next Pointer Register, page 185

Power Management Next Ptr

01

—

N

Y

DD

E4

—

N

N

DF:DE

Power Management Capabilities

Register, page 186

0001

Y

Secondary

Y

E1:E0

Power Management Control and

Status Register, page 187

0000

Y

Y

Y

E2

PMCSR Bridge Support

Extensions, page 187

00

—

N

Y

E3

Power Management Data

Register, page 188

00

Y

N

Y

E4

Vital Product Data (VPD) ECP ID

and Next Pointer Register, page

192

VPD Cap ID

VPD Next Ptr

04

—

N

Y

E5

EC

—

N

N

E7:E6

Vital Product Data (VPD)

Address Register, page 193

VPD Address

Indeterminate

—

Y

Y

EB:E8

VPD Data

Indeterminate

—

Y

Y

Table 32. Configuration Space Address Register (Sheet 4 of 5)

Byte

Offset

(Hex)

Register Name

Reset Value

(Hex)

Preload

Write

Access

Read

Access