3 secondary pci bus interface signals, Secondary pci bus interface signals – Intel 21555 User Manual

Page 28

28

21555 Non-Transparent PCI-to-PCI Bridge User Manual

Signal Descriptions

3.3

Secondary PCI Bus Interface Signals

describes the secondary PCI bus interface signals. The letters in the “Type” column are described in

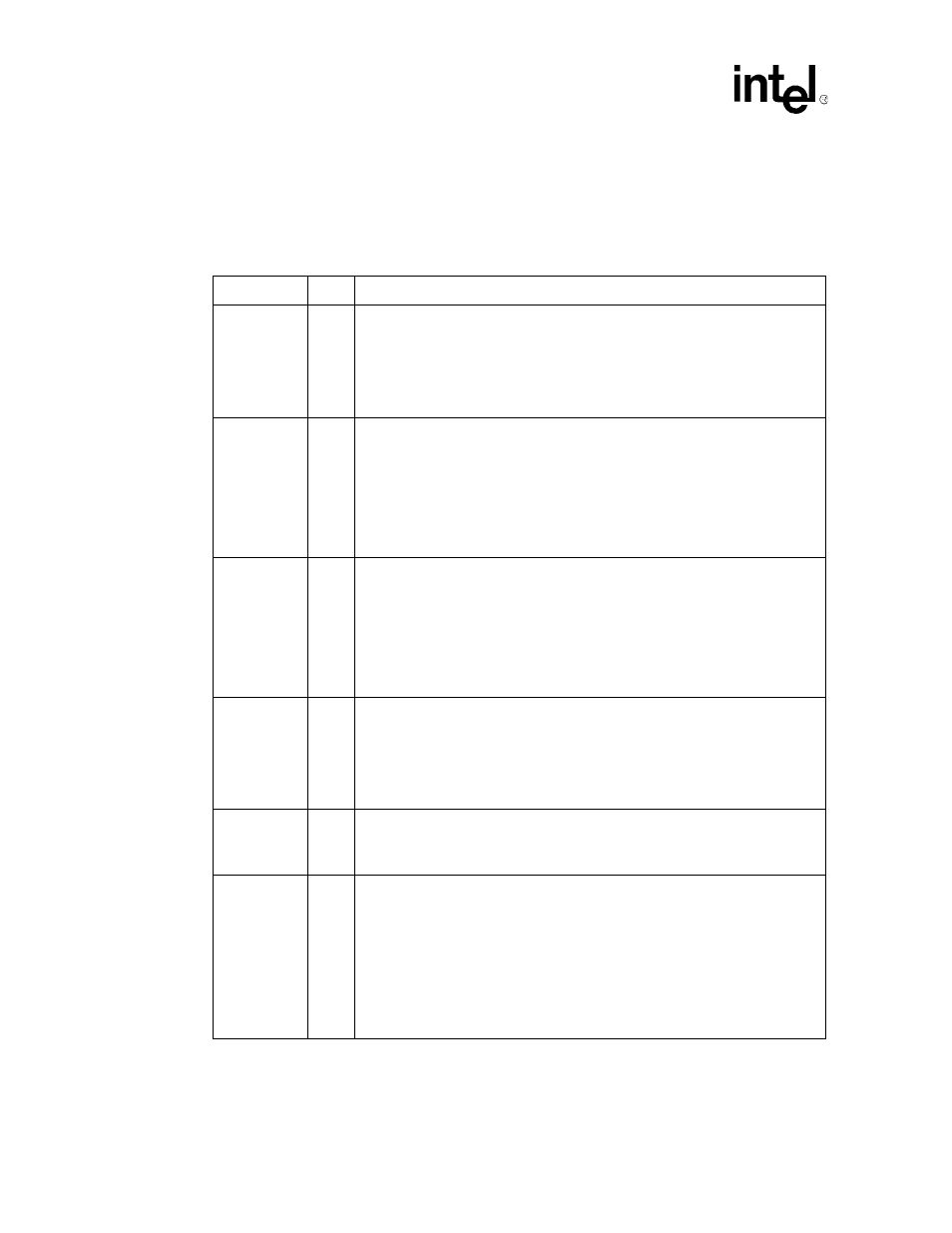

Table 8. Secondary PCI Bus Interface Signals (Sheet 1 of 2)

Signal Name

Type

Description

s_ad[31:0]

TS

Secondary PCI interface address and data. These signals are a 32-bit multiplexed

address and data bus. During the address phase or phases of a transaction, the

initiator drives a physical address on s_ad[31:0]. During the data phases of a

transaction, the initiator drives write data, or the target drives read data, on

s_ad[31:0].

When the secondary PCI bus is idle, the 21555 drives s_ad to a valid logic level

when its secondary bus grant is asserted.

s_cbe_l[3:0]

TS

Secondary PCI interface command and byte enables. These signals are a

multiplexed command field and byte enable field. During the address phase or

phases of a transaction, the initiator drives the transaction type on s_cbe_l[3:0].

When there are two address phases, the first address phase carries the

dual-address command and the second address phase carries the transaction type.

For both read and write transactions, the initiator drives byte enables on

s_cbe_l[3:0] during the data phases.

When the secondary PCI bus is idle, the 21555 drives s_cbe_l to a valid logic level

when its secondary bus grant is asserted.

s_devsel_l

STS

Secondary PCI interface DEVSEL#. Signal s_devsel_l is asserted by the target,

indicating that the device is responding to the transaction. As a target, the 21555

decodes the address of a transaction initiated on the secondary bus to determine

whether to assert s_devsel_l. As an initiator of a transaction on the secondary bus,

the 21555 looks for the assertion of s_devsel_l within five clock cycles of

s_frame_l assertion; otherwise, the 21555 terminates the transaction with a master

abort.

Upon completion of a transaction, s_devsel_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

s_frame_l

STS

Secondary PCI interface FRAME#. Signal s_frame_l is driven by the initiator of a

transaction to indicate the beginning and duration of an access on the secondary

PCI bus. Signal s_frame_l assertion (falling edge) indicates the beginning of a PCI

transaction. While s_frame_l remains asserted, data transfers can continue. The

deassertion of s_frame_l indicates the final data phase requested by the initiator.

Upon completion of a transaction, s_frame_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.

s_idsel

I

Secondary PCI interface IDSEL. Signal s_idsel is used as the chip select line for

Type 0 configuration accesses to 21555 configuration space from the secondary

bus. When s_idsel is asserted during the address phase of a Type 0 configuration

transaction, the 21555 responds to the transaction by asserting s_devsel_l.

s_irdy_l

STS

Secondary PCI interface IRDY#. Signal s_irdy_l is driven by the initiator of a

transaction to indicate the initiator’s ability to complete the current data phase on the

secondary PCI bus.

During a write transaction, assertion of s_irdy_l indicates that valid write data is

being driven on the s_ad bus.

During a read transaction, assertion of s_irdy_l indicates that the initiator is able to

accept read data for the current data phase. Once asserted during a given data

phase, s_irdy_l is not deasserted until the data phase completes.

Upon completion of a transaction, s_irdy_l is driven to a deasserted state for one

clock cycle and is then sustained by an external pull-up resistor.