Intel 21555 User Manual

Page 137

21555 Non-Transparent PCI-to-PCI Bridge User Manual

137

List of Registers

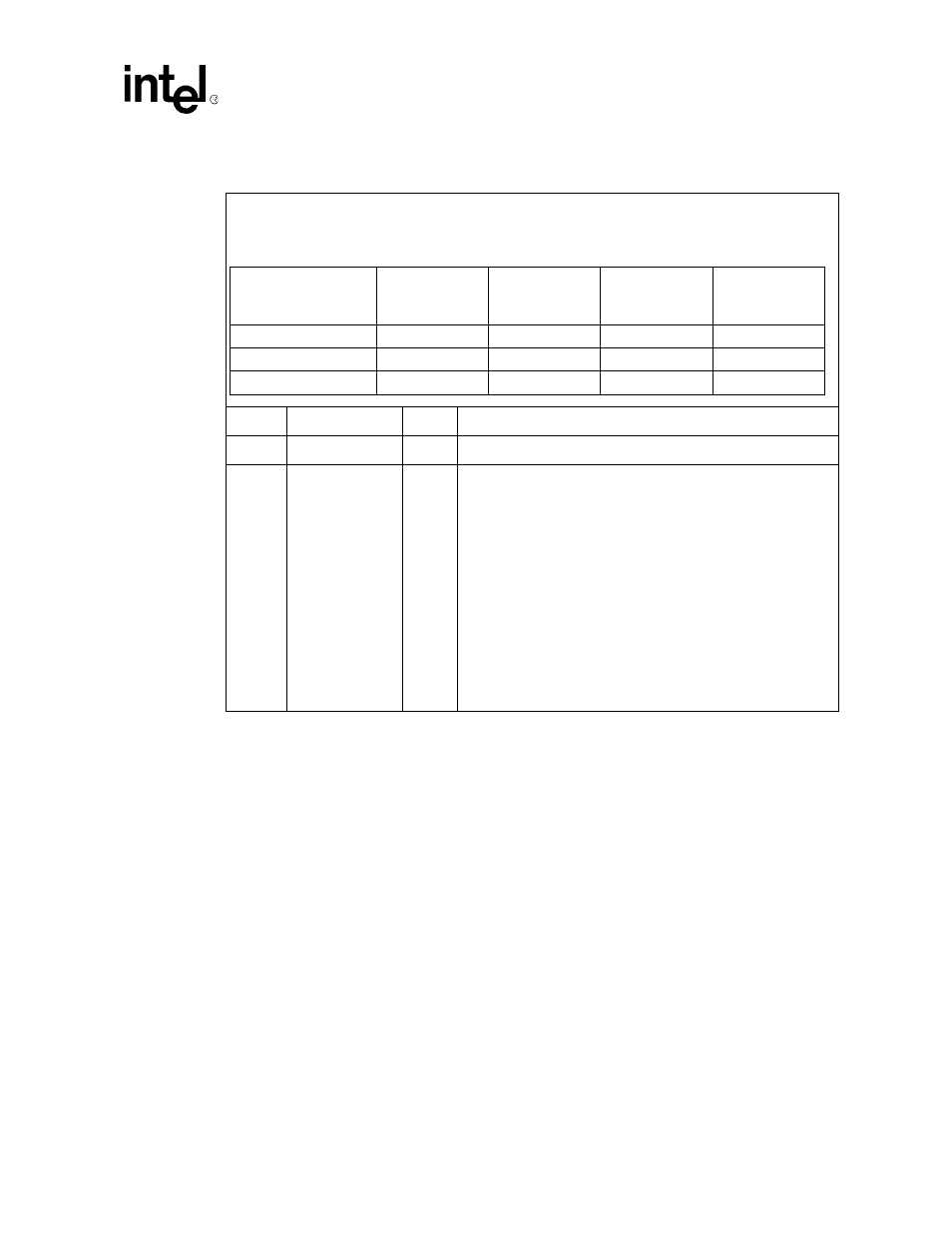

Table 42. Downstream Memory 0, 2, 3, and Upstream Memory 1 Translated Base Register

These registers contain the translated base addresses for their respective downstream and upstream BARs.

The base address of the transaction on the initiator bus is replaced by the base address contained in these

registers

These registers are also mapped in the

21555

I/O and memory CSR space.

Bit

Name

R/W

Description

11:0

Reserved

R

Reserved. Returns 0 when read.

31:12

XLAT_BASE

R/W

Contains the translated base address for downstream or upstream

transactions whose initiator bus addresses fall into one of the

following address ranges:

•

Downstream Memory 0 (above low 4K boundary)

•

Downstream Memory 2

•

Downstream Memory 3

•

Upstream Memory 1

The number of bits that are used for the translated base is

determined by the setup register corresponding to that base

address and also matches the number of writable bits in the

corresponding BAR.

The remaining bits can be written but are ignored when performing

address translation. When a memory transaction is initiated by the

21555 on the target bus, the original base address is replaced with

the value contained in this register.

Offsets

Downstream

Memory 0

Translated Base

Downstream

Memory 2

Translated Base

Downstream

Memory 3

Translated Base

Upstream

Memory 1

Translated Base

Primary byte

97:94h

9F:9Ch

A3:A0h

AB:A8h

Secondary byte

97:94h

9F:9Ch

A3:A0h

AB:A8h

CSR byte

06B:068h

073:070h

077:074h

07F:07Ch