Intel 21555 User Manual

Page 139

21555 Non-Transparent PCI-to-PCI Bridge User Manual

139

List of Registers

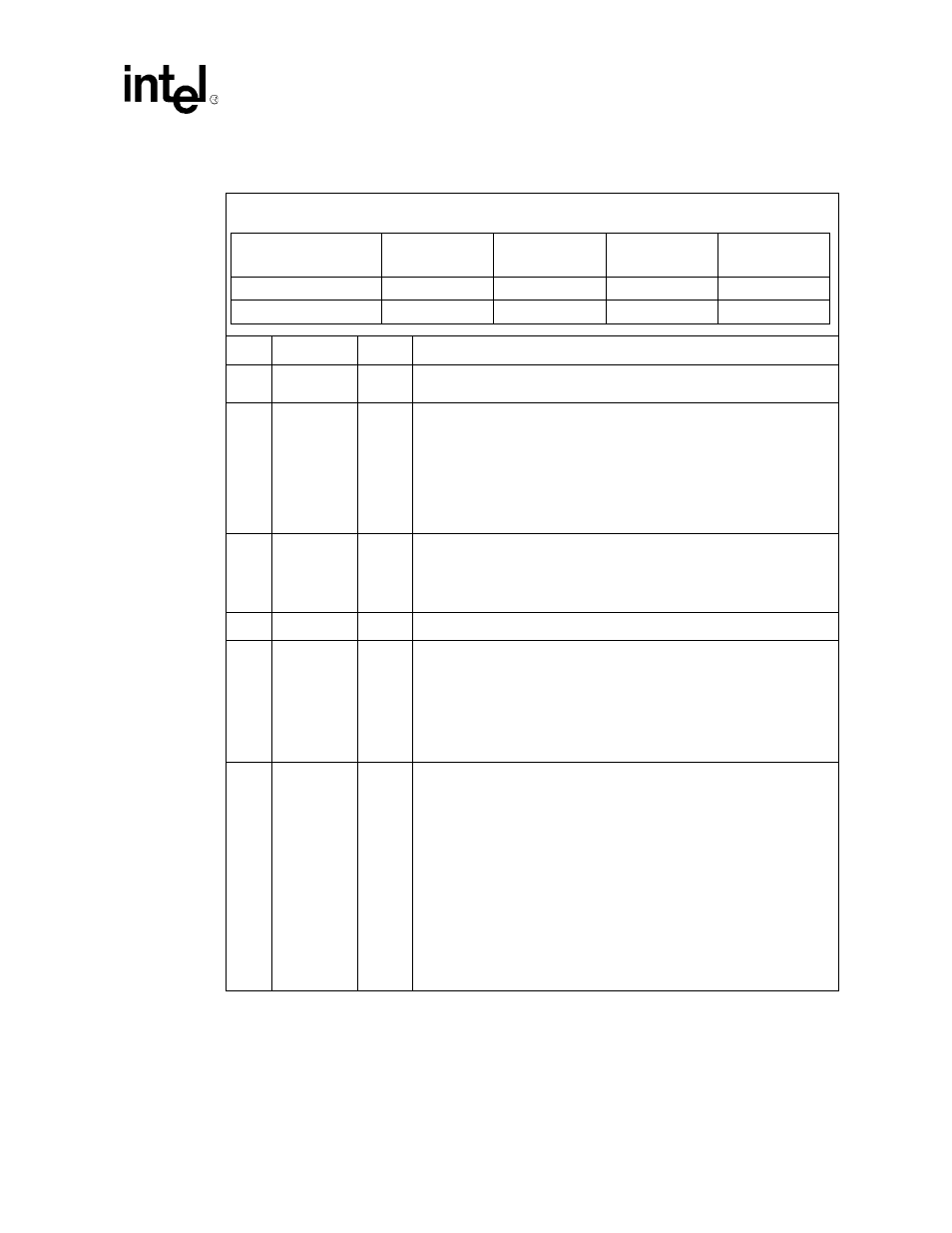

Table 44. Downstream Memory 0, 2, 3, and Upstream Memory 1 Setup Registers

These registers are used to program the type and size of their respective upstream and

downstream BARs.

Bit

Name

R/W

Description

0

Type

Selector

R

Read only as 0 to indicate memory space is requested by the

corresponding memory BAR.

2:1

Type

R/(WS)

Type of space requested. Allowable values are:

•

00b to indicate that the space requested by the BAR may be located

anywhere in memory space

•

01b to indicate that it must be mapped below a 1MB boundary

•

10b for Downstream Memory 3 Setup register to request a 64

-

bit BAR

Other values may yield unpredictable results.

Reset value is 00b.

3

Prefetchable

R/(WS)

Indicates whether the space requested by the BAR is prefetchable.

•

When 0, not prefetchable.

•

When 1, prefetchable.

•

Reset value is 0

11:4

Reserved

R

Read only as 0.

30:12

Size

R/(WS)

These bits specify the size of the address range requested by the BAR.

•

When a bit is 1, the corresponding bit in the BAR functions as a

readable and writable bit.

•

When a bit is 0, the corresponding bit in the BAR functions as a

read

-

only bit that always returns zero when read.

•

Reset value is 0 (disabled), except for Downstream Memory 0 Setup

register, whose reset value is 7FFFFh (request 4 KB).

31

BAR_Enable

R/(WS)

BAR enable.

Bit [31] of the Downstream Memory 0 Setup register always reads as 1,

indicating that the BAR cannot be disabled. When a bus master attempts to

write this bit with a 0, the 21555 returns all bits {31:12] of the setup register

as 1s (request 4KB).

•

When the Upper 32 Bits Downstream Memory 3 Setup register bit [31]

is a 1, the corresponding BAR is enabled as a 64

-

bit register, and this

bit is part of the size field for the 64

-

bit BAR.

•

When 0, the corresponding BAR is disabled and reads as 0, with the

exception noted above.

•

When 1, the corresponding BAR is enabled, with size and type

specified by this setup register.

•

Reset value is 0, except for Downstream Memory 0 Setup register that

has a reset value of 1.

Offsets

Downstream

Memory 0 Setup

Downstream

Memory 2 Setup

Downstream

Memory 3 Setup

Upstream

Memory 1 Setup

Primary byte

AF:ACh

B7:B4h

BB:B8h

CB:C8h

Secondary byte

AF:ACh

B7:B4h

BB:B8h

CB:C8h