Primary and secondary class code registers, Primary and secondary cache line size registers – Intel 21555 User Manual

Page 152

152

21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

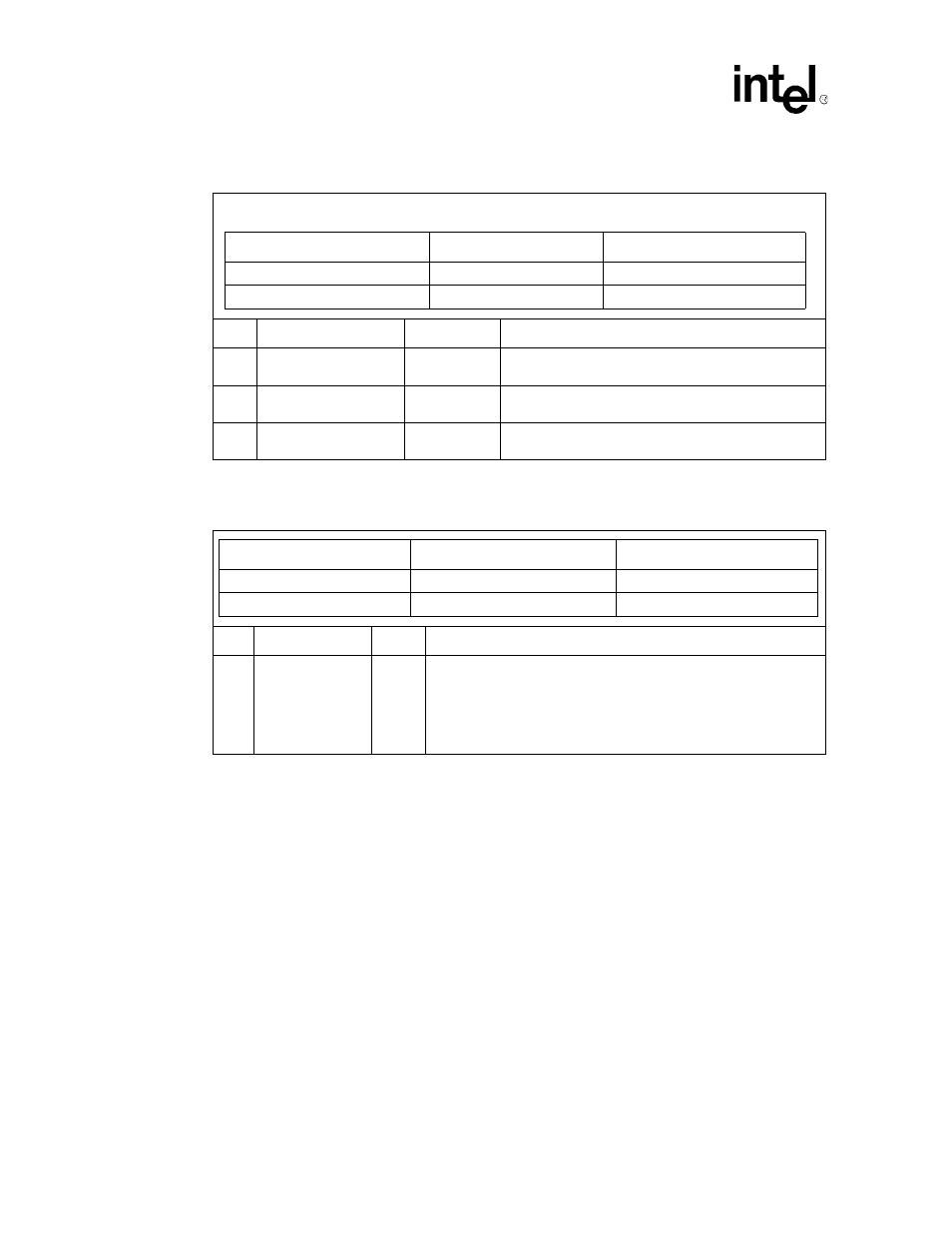

Table 64. Primary and Secondary Class Code Registers

These registers may be preloaded through the serial ROM. The Primary Class Code register may also be

programmed by the local processor before host configuration

.

Bit

Name

R/W

Description

7:0

Prog IF (PIF)

PPIF: R/(WS)

SPIF: R

Reads as zero.

15:8

Sub

-

Class Code (SCC)

PSCC: R/(WS)

SSCC: R

Reads as 80 hex to indicate that this bridge device is

classified as “other”.

23:16

Base Class Code (BCC)

PBCC:R/(WS)

SBCC: R

Reads as 06 hex to indicate device is a bridge device.

Table 65. Primary and Secondary Cache Line Size Registers

Bit

Name

R/W

Description

7:0

Cache Line Size

R/W

Designates the cache line size for the corresponding interface in units

of 32

-

bit Dwords. Used for prefetching memory reads and for

terminating MWIs. Valid cache line sizes are 8, 16, and 32 Dwords.

When the cache line size is set to any other value, the 21555 uses the

same behavior as when the cache line size is set to 8.

Reset value is 00h.

Offsets

Primary Class Code

Secondary Class Code

Primary byte

0B:09h

4B:49h

Secondary byte

4B:49h

0B:09h

Offsets

Primary Cache Line Size

Secondary Cache Line Size

Primary byte

0Ch

4Ch

Secondary byte

4Ch

0Ch