Intel 21555 User Manual

Page 181

21555 Non-Transparent PCI-to-PCI Bridge User Manual

181

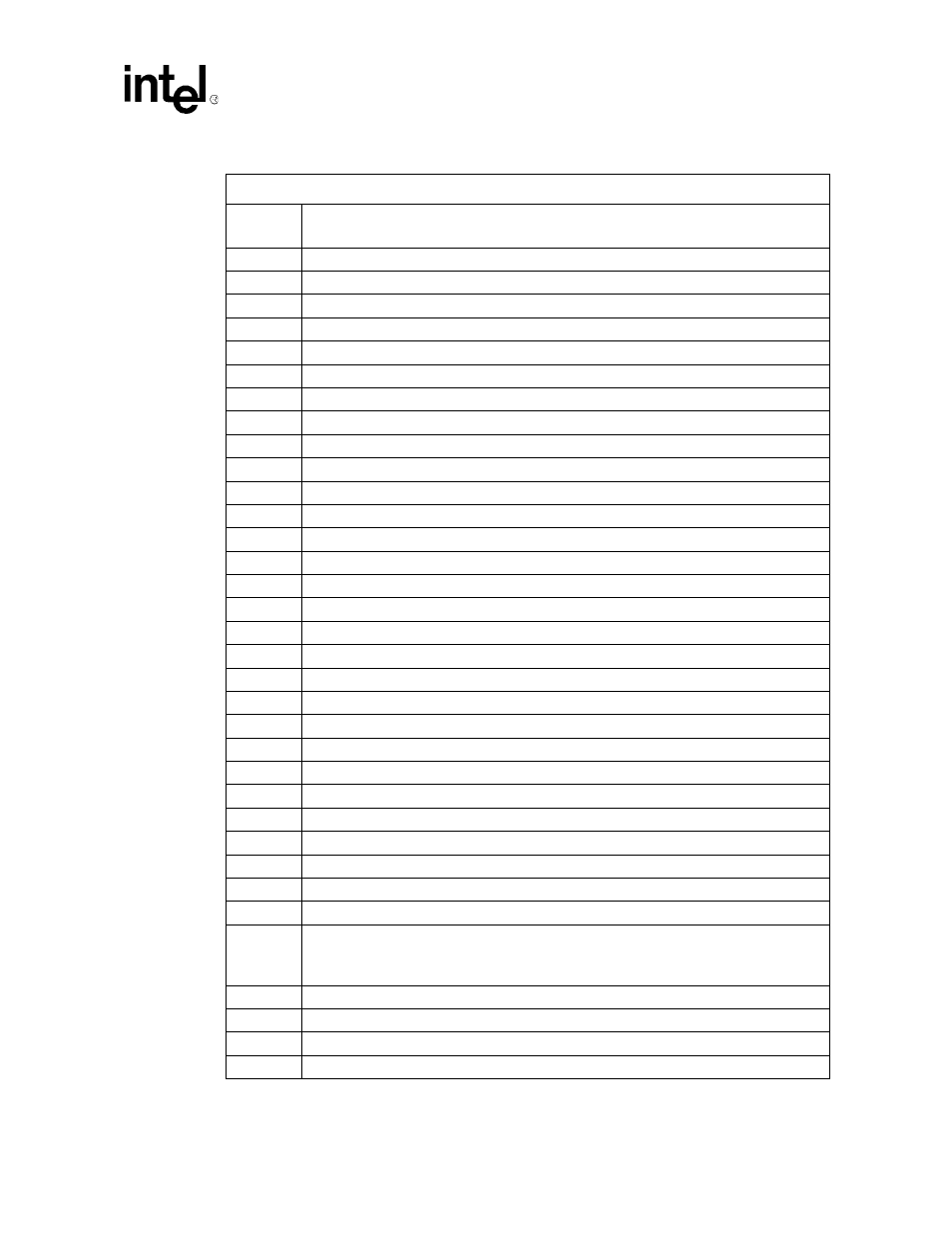

List of Registers

09h

Subsystem ID [7:0]

0Ah

Subsystem ID [15:8]

0Bh

Primary Minimum Grant

0Ch

Primary Maximum Latency

0Dh

Secondary Programming Interface

0Eh

Secondary Sub

-

Class Code

0Fh

Secondary Base Class Code

10h

Secondary Minimum Grant

11h

Secondary Maximum Latency

12h

Downstream Memory 0 Setup [7:0]. Bits [0, 7:4] are not loaded and should be 0.

13h

Downstream Memory 0 Setup [15:8]. Bits [11:8] are not loaded and should be 0.

14h

Downstream Memory 0 Setup [23:16]

15h

Downstream Memory 0 Setup [31:24]

16h

Downstream I/O or Memory 1 Setup [7:0]. Bits [5:4] are not loaded and should be 0.

17h

Downstream I/O or Memory 1 Setup [15:8]

18h

Downstream I/O or Memory 1 Setup [23:16]

19h

Downstream I/O or Memory 1 Setup [31:24]

1Ah

Downstream Memory 2 Setup [7:0]. Bits [0, 7:4] are not loaded and should be 0.

1Bh

Downstream Memory 2 Setup [15:8]. Bits [11:8] are not loaded and should be 0.

1Ch

Downstream Memory 2 Setup [23:16]

1Dh

Downstream Memory 2 Setup [31:24]

1Eh

Downstream Memory 3 Setup [7:0]. Bits [0, 7:4] are not loaded and should be 0.

1Fh

Downstream Memory 3 Setup [15:8]. Bits [11:8] are not loaded and should be 0.

20h

Downstream Memory 3 Setup [23:16]

21h

Downstream Memory 3 Setup [31:24]

22h

Downstream Memory 3 Setup Upper 32 Bits [7:0]

23h

Downstream Memory 3 Setup Upper 32 Bits [15:8]

24h

Downstream Memory 3 Setup Upper 32 Bits [23:16]

25h

Downstream Memory 3 Setup Upper 32 Bits [31:24]

26h

•

Bit [0]: Primary Expansion ROM Setup [24] (enable)

•

Bits [3:1]: Not loaded. Should be 0.

•

Bits [7:4]: Primary Expansion ROM Setup [15:11]

27h

Primary Expansion ROM Setup [23:16]

28h

Upstream I/O or Memory 0 Setup [7:0]. Bits [5:4] are not loaded and should be 0.

29h

Upstream I/O or Memory 0 Setup [15:8]

2Ah

Upstream I/O or Memory 0 Setup [23:16]

Table 114. Serial Preload Sequence (Sheet 2 of 3)

Not all of the bits in the sequence are used. Bits that are not used must be 0 (zero)

Byte

offset

Description