Intel 21555 User Manual

Page 129

21555 Non-Transparent PCI-to-PCI Bridge User Manual

129

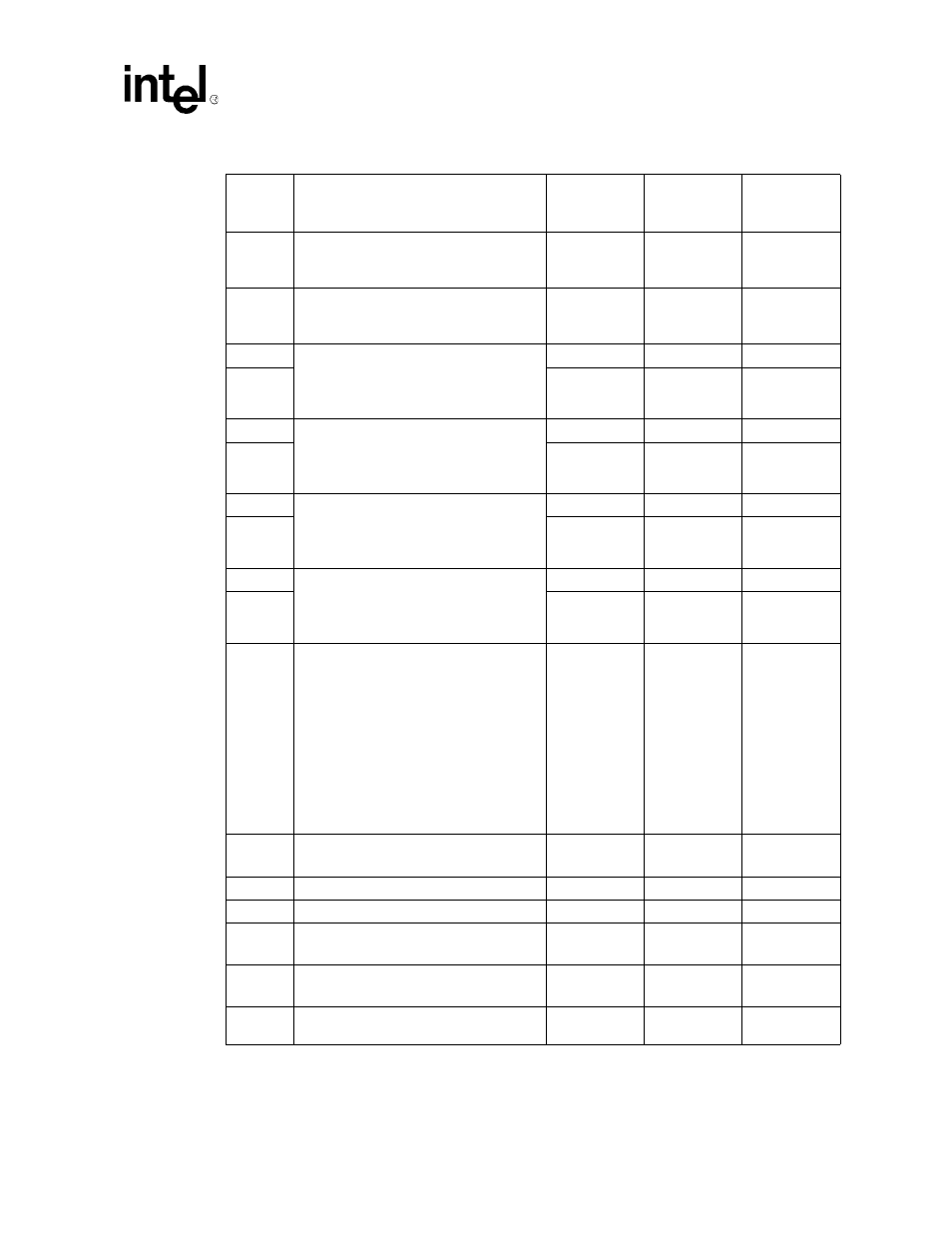

List of Registers

093:090

Upstream Page Boundary IRQ Mask 0

Register, page 172

Upstream Page Boundary IRQ Mask 0

FFFFFFFF

Y

Y

097:094

Upstream Page Boundary IRQ Mask 1

Register, page 172

Upstream Page Boundary IRQ Mask 1

FFFFFFFF

Y

Y

099:098

Primary Clear IRQ and Secondary Clear

IRQ Registers, page 173

Primary Clear IRQ

Secondary Clear IRQ

0000

W1TC

Y

09B:09A

0000

W1TC

Y

09D:09C

Primary Set IRQ and Secondary Set IRQ

Registers, page 173

Primary Set IRQ

Secondary Set IRQ

0000

W1TS

Y

09F:09E

0000

W1TS

Y

0A1:0A0

Primary Clear IRQ Mask and Secondary

Clear IRQ Mask Registers, page 174

Primary Clear IRQ Mask

Secondary Clear IRQ Mask

FFFF

W1TC

Y

0A3:0A2

FFFF

W1TC

Y

0A5:0A4

Primary Set IRQ Mask and Secondary Set

IRQ Mask Registers, page 174

Primary Set IRQ Mask

Secondary Set IRQ Mask

FFFF

W1TS

Y

0A7:0A6

FFFF

W1TS

Y

0AB:0A8

0AF:0AC

0B3:0B0

0B7:0B4

0BB:0B8

0BF:0BC

0C3:0C0

0C7:0C4

Scratchpad 0 Through Scratchpad 7

Registers, page 174

Scatchpad 0

Scatchpad 1

Scatchpad 2

Scatchpad 3

Scatchpad 4

Scatchpad 5

Scatchpad 6

Scatchpad 7

Indeterminate

Y

Y

0C9:0C8

ROM Setup

7E00

Y

Y

0CA

ROM Data

Indeterminate

Y

Y

0CB

Reserved

00

N

Y

0CE:0CC

ROM Address Register, page 178

ROM Address

000400

Y

Y

0CF

ROM Control Register, page 178

ROM Control

0000

Y

Y

0D2:0D0

Generic Own Bits Register, page

164

Generic Own Bits

TBD

TBD

TBD

Table 33. CSR Address Map (Sheet 4 of 5)

Byte

Offset

(Hex)

Register Name

Reset Value

Write Access

Read Access