4 address decoding, 1 primary and secondary address, Primary csr and downstream memory 0 bar – Intel 21555 User Manual

Page 130

130

21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

16.4

Address Decoding

16.4.1

Primary and Secondary Address

This section covers pages

and includes tables

through

. See

for theory of operation information.

0FF:0D0

Reserved

00000000

N

Y

1FF:100

Upstream Memory 2 Lookup Table, page

147

Upstream Memory 2 Look-up Table

Indeterminate

Y

Y

FFF:200

Reserved

00000000

N

Y

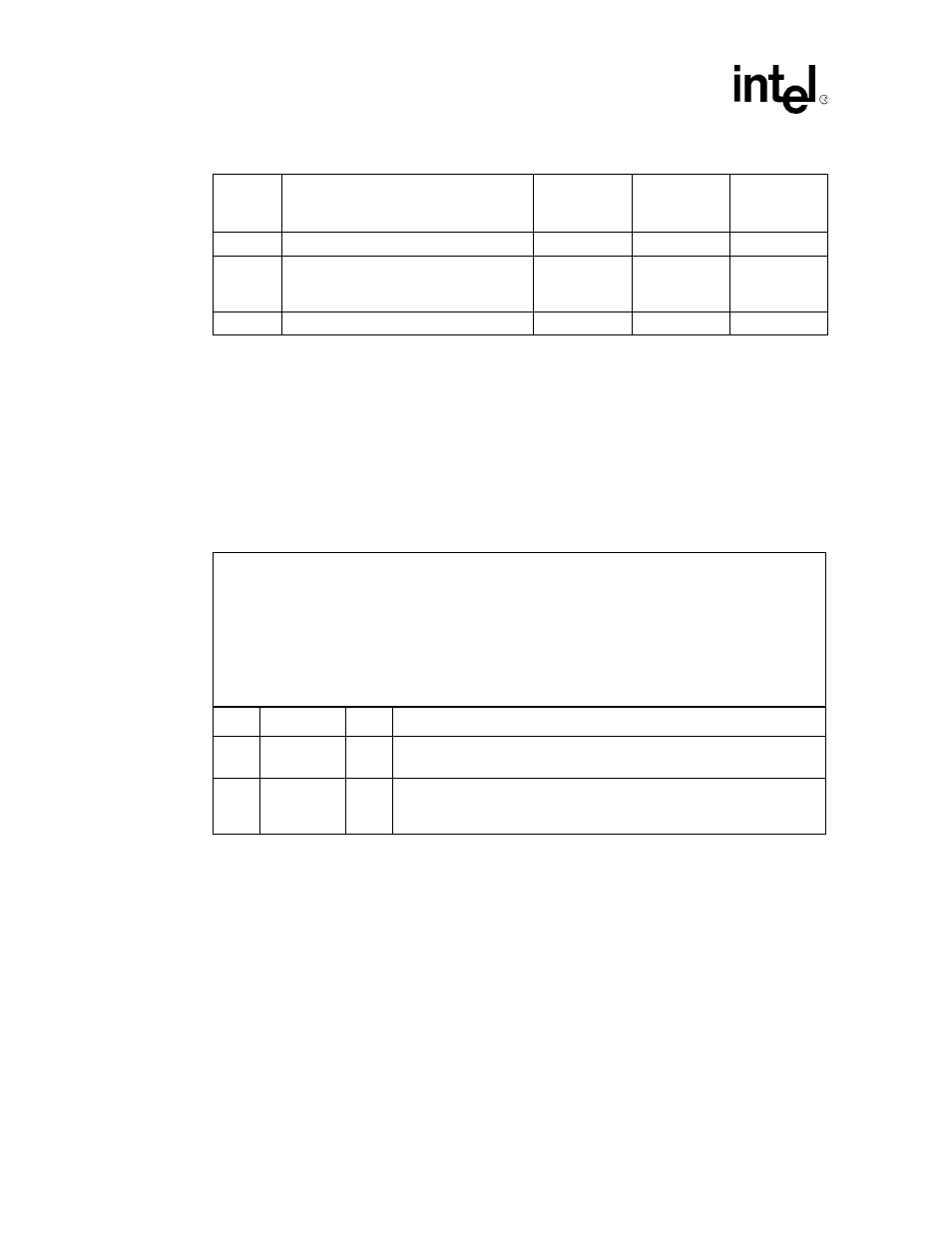

Table 34. Primary CSR and Downstream Memory 0 Bar

a

(Sheet 1 of 2)

•

Primary byte offset: 13:10h

•

Secondary byte offset: 53:50h

The Primary CSR and Downstream Memory 0 BARs map the 21555 registers into primary memory space.

They can specify a downstream memory range for forwarding of memory transactions.

To specify a downstream forwarding range, load the Downstream Memory 0 Setup Register from the optional

SROM or the local processor This load must occur before configuration software running on the host

processor can access this register.

Local processor access of the setup register should be done before the Primary Lockout Reset Value bit is

cleared.

Bit

Name

R/W

Description

0

Space

Indicator

R

Indicates the type of address space to setup.

When 0, it indicates that memory space is requested.

2:1

Type

R

Indicates size and location of this address space.

Reset value is To 00 indicating that this space can be mapped anywhere in

32-bit memory.

Table 33. CSR Address Map (Sheet 5 of 5)

Byte

Offset

(Hex)

Register Name

Reset Value

Write Access

Read Access