4 secondary pci bus interface 64, Bit extension signals – Intel 21555 User Manual

Page 30

30

21555 Non-Transparent PCI-to-PCI Bridge User Manual

Signal Descriptions

3.4

Secondary PCI Bus Interface 64

-

Bit Extension

Signals

describes the secondary PCI bus interface 64-bit extension signals. The letters in the “Type” column are

.

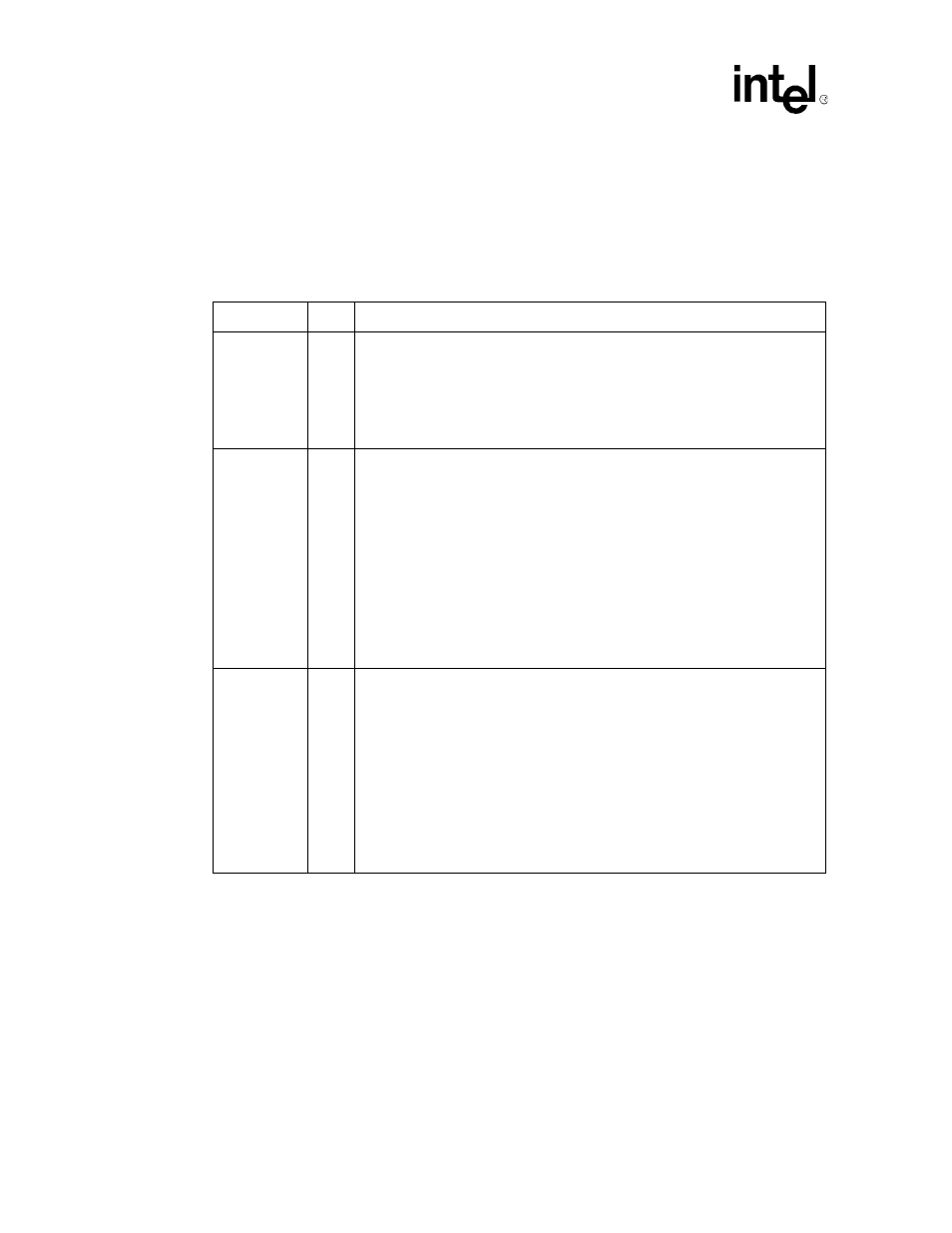

Table 9. Secondary PCI Bus Interface 64

-

Bit Extension Signals (Sheet 1 of 2)

Signal Name

Type

Description

s_ack64_l

STS

Secondary PCI interface acknowledge 64-bit transfer.

Signal s_ack64_l should never be driven when s_req64_l is not driven.

Signal s_ack64_l is asserted by the target only when s_req64_l is asserted by the

initiator, to indicate the target’s ability to transfer data using 64 bits.

Signal s_ack64_l has the same timing as s_devsel_l. When deasserting,

s_ack64_l is driven to a deasserted state for one clock cycle and is then sustained

by an external pull-up resistor.

s_ad[63:32]

TS

Secondary PCI interface address and data upper 32 bits.

The 21555 does not bus park these pins. These pins are tristated during the

assertion of s_rst_l. Signals s_ad[63:32] are driven to a valid value when the 64-bit

extension is disabled (s_req64_l is deasserted during s_rst_l assertion).

This multiplexed address and data bus provides an additional 32 bits to the

secondary interface. During the address phase or phases of a transaction, when the

dual-address command is used and s_req64_l is asserted, the initiator drives the

upper 32 bits of a 64-bit address; otherwise, these bits are undefined, and the

initiator drives a valid logic level onto the pins. During the data phases of a

transaction, the initiator drives the upper 32 bits of 64-bit write data, or the target

drives the upper 32 bits of 64-bit read data, when s_req64_l and s_ack64_l are

both asserted.

When not driven, signals s_ad[63:32] are pulled up to a valid logic level through

external resistors.

s_cbe_l[7:4]

TS

Secondary PCI interface command and byte enables upper 4 bits.

The 21555 does not bus park these pins. These pins are tristated during the

assertion of s_rst_l. Signals s_cbe_l[7:4] are driven to a valid value when the

64-bit extension is disabled (s_req64_l is deasserted during s_rst_l assertion).

These signals are a multiplexed command field and byte enable field. During the

address phase or phases of a transaction, when the dual-address command is used

and s_req64_l is asserted, the initiator drives the transaction type on s_cbe_l[7:4];

otherwise, these bits are undefined, and the initiator drives a valid logic level onto

the pins. For both read and write transactions, the initiator drives byte enables for

the s_ad[63:32] data bits on s_cbe_l[7:4] during the data phases, when s_req64_l

and s_ack64_l are both asserted.

When not driven, signals s_cbe_l[7:4] are pulled up to a valid logic level through

external resistors.