7 interrupt registers, Interrupt registers, Chip status csr – Intel 21555 User Manual

Page 170: Chip set irq mask register

170

21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

16.7

Interrupt Registers

This section contains information about interrupt registers. See

for theory of operation information.

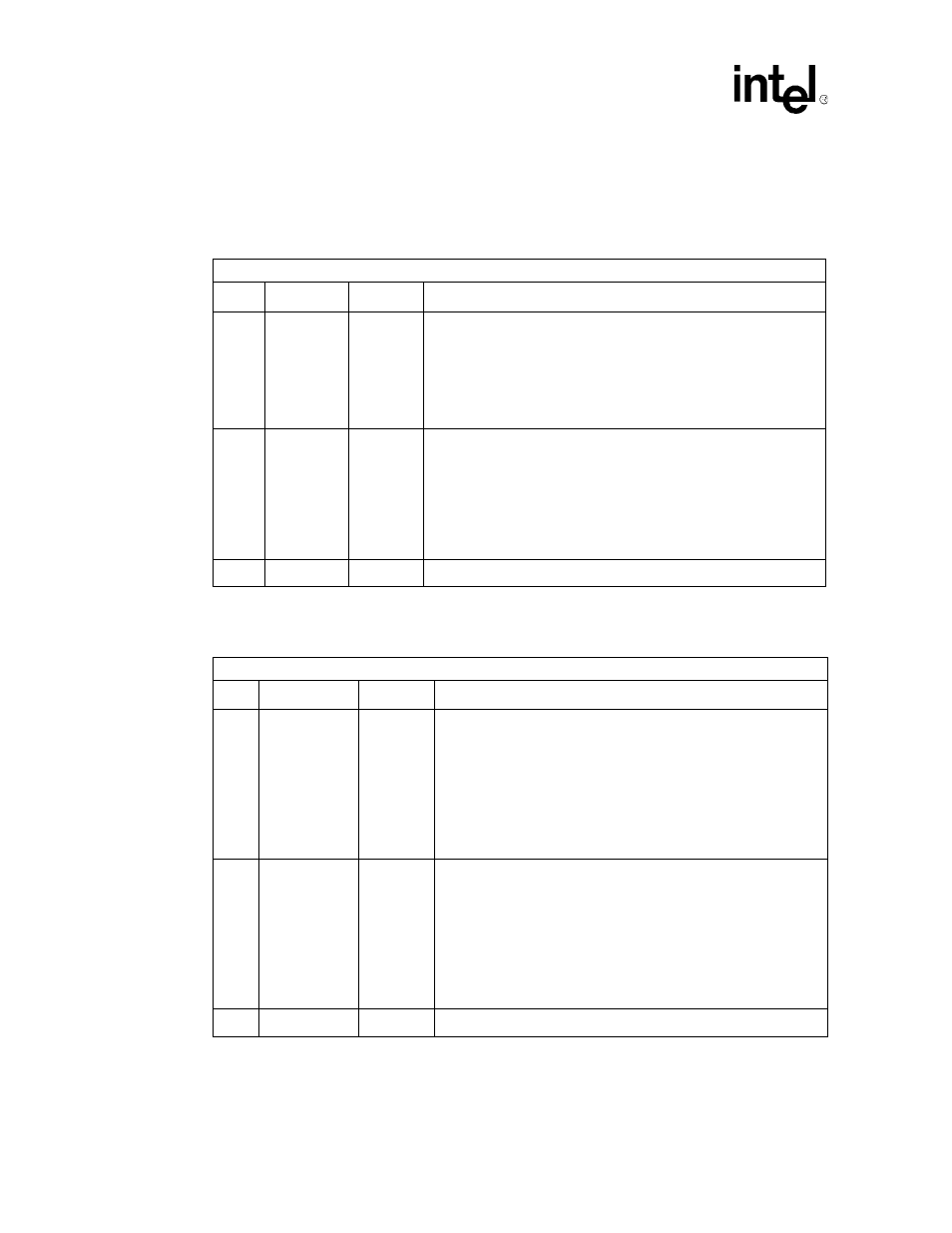

Table 95. Chip Status CSR

Byte Offsets: 083:082h

Bit

Name

R/W

Description

0

PM_D0

R/W1TC

Power Management Transition to D0. The 21555 sets this bit when it is

transitioned from a low power D1 or D2 state to a high power D0 state.

When the corresponding Chip IRQ Mask bit for this event is a 0, the

21555 asserts s_inta_l to indicate to the subsystem that it is being

brought to a higher power state.

Writing a 1 clears this bit to a 0. Writing a 0 has no effect.

Reset value is 0

1

Subsystem

Event

R/W1TC

Generic subsystem event bit. The 21555 sets this bit when a

deasserting (rising) edge is detected on s_pme_l. When s_pme_l is

not used for power management purposes, it may be used to signal

some other subsystem event. When the Chip IRQ Mask bit for this

event is a 0, the 21555 asserts p_inta_l to indicate to the host system

that this signal was deasserted.

Writing a 1 clears this bit to a 0. Writing a 0 has not effect.

Reset value is 0

15:2

Reserved

R

Reserved. Returns 0 when read.

Table 96. Chip Set IRQ Mask Register

Byte Offsets: 085:084h

Bit

Name

R/W

Description

0

Set_D0M

R/W1TS

•

When 0, signal s_inta_l is asserted on the 21555’s secondary

interface when the corresponding chip event bit is a 1, indicating

a return of power state to D0.

•

When 1, the corresponding chip event bit does not generate an

interrupt.

Writing a 1 to a bit in this register sets the Chip IRQ Mask bit to 1.

Writing a 0 to any bit in this register has no effect. Reading this

register returns the current status of the Chip IRQ Mask bits.

•

Reset value is 1

1

Set_Sstat

R/W1TS

•

When 0, signal p_inta_l is asserted on the 21555’s primary

interface when the corresponding chip event bit is a 1, indicating

a deasserting edge on s_pme_l.

•

When 1, the corresponding chip event bit does not generate an

interrupt.

Writing a 1 to a bit in this register sets the Chip IRQ Mask bit to 1.

Writing a 0 to any bit in this register has no effect. Reading this

register returns the current status of the Chip IRQ Mask bits.

•

Reset value is 1

15:2

Reserved

R

Reserved. Returns 0 when read.