3 lookup table based address translation, Lookup table based address translation, Direct offset address translation – Intel 21555 User Manual

Page 37: Downstream address translation example, Section 4.3.3, Figure 5

21555 Non-Transparent PCI-to-PCI Bridge User Manual

37

Address Decoding

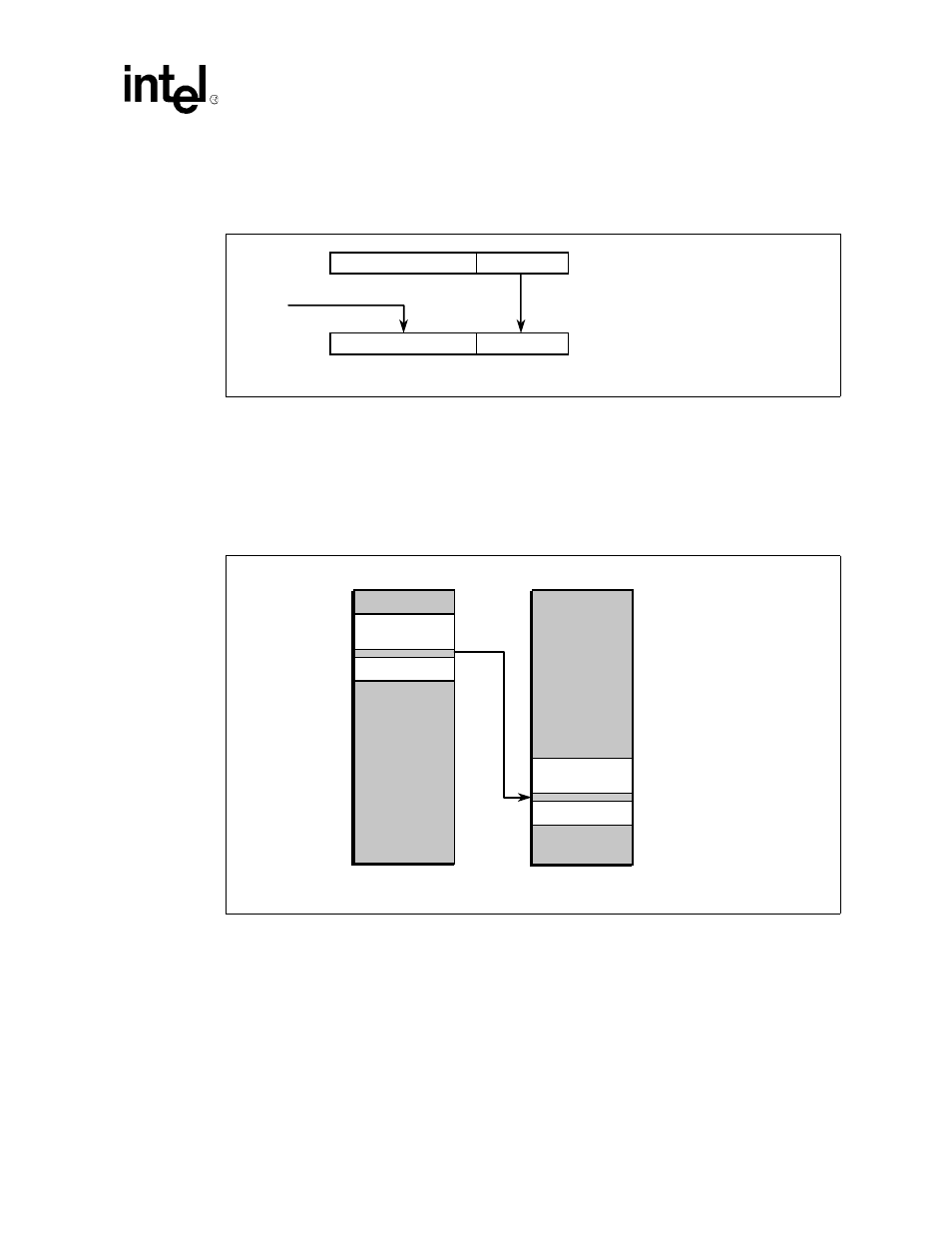

This new base address, also called the translated base address, references a new location in the

secondary bus address map. The offset is not affected. The process is similar for transactions

forwarded from the secondary bus to the primary bus.

Each memory address range using direct offset address translation has its own translated base. The translated base

addresses are programmable in registers corresponding to each BAR. These registers are mapped both in

device-specific configuration space and in CSR space. The number of bits of the translated base address

corresponds to the number of writable bits in the respective BAR. Likewise, the number of bits of the offset also

varies and depends on the size of the BAR.

shows an example of address translation of downstream

memory transactions. Again, upstream transactions are treated similarly.

4.3.3

Lookup Table Based Address Translation

As mentioned in

, Upstream Memory 2 address translation is treated differently than the other ranges.

The 21555 uses a page size based lookup table to perform address translation for transactions falling into this range.

A lookup table provides a flexible way of translating secondary bus local addresses to primary bus system

addresses.

Figure 5. Direct Offset Address Translation

Figure 6. Downstream Address Translation Example

A7463-01

Translated Base

Translated Address

Offset

Base

Original Address

Offset

A7464-01

Base + Offset

Translated

Base + Offset

Primary Address Map

Secondary Address Map