Primary interface configuration space address map, Vendor id register, Device id register – Intel 21555 User Manual

Page 148: Table 60, Table 57, List of registers, Table 59. vendor id register, Table 60. device id register

148

21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

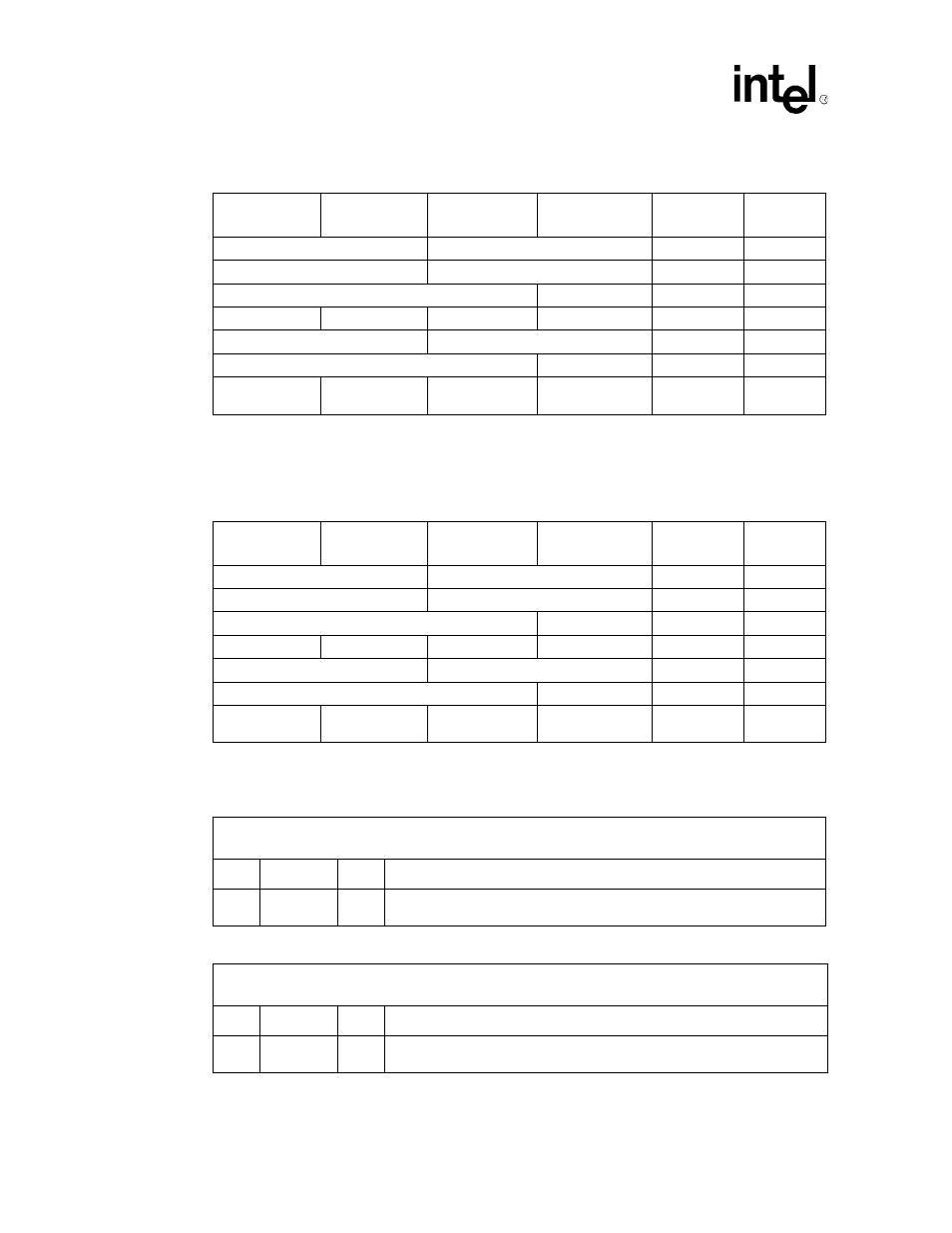

Table 57. Primary Interface Configuration Space Address Map

Byte 3

Byte 2

Byte 1

Byte 0

Primary

Offset

Secondary

Offset

Device ID

Vendor ID

00h

40h

Primary Status

Primary Command

04h

44h

Primary Class Code

Revision ID

08h

48h

BIST

,

Header Type

Primary MLT

Primary CLS

0Ch

4Ch

Subsystem ID

Subsystem Vendor ID

2Ch

6Ch

Reserved

Cap_Ptr

34h

74h

Primary

Max_Lat

Primary

Min_Gnt

Primary Interrupt

Pin

Primary Interrupt

Line

3Ch

7Ch

1. Primary and secondary configuration registers are shared.

2. Register or a portion of the register may be preloaded using the serial ROM interface.

Table 58. Secondary Interface Configuration Space Address Map

Byte 3

Byte 2

Byte 1

Byte 0

Primary

Offset

Secondary

Offset

Device ID

Vendor ID

40h

00h

Secondary Status

Secondary Command

44h

04h

Secondary Class Code

Revision ID

48h

08h

BIST

,

Header Type

Secondary MLT

Secondary CLS

4Ch

0Ch

Subsystem ID

Subsystem Vendor ID

6Ch

2Ch

Reserved

Cap_Ptr

74h

34h

Secondary

Max_Lat

Secondary

Min_Gnt

Secondary

Interrupt Pin

Secondary

Interrupt Line

7Ch

3Ch

1. Primary and secondary configuration registers are shared.

2. Register or a portion of the register may be preloaded using the serial ROM interface.

Table 59. Vendor ID Register

•

Primary byte offset: 01:00h and 41:40h

•

Secondary byte offset: 41:40h and 01:00h

Bit

Name

R/W

Description

15:0

Vendor ID

R

The Vendor ID identifies Intel

®

as the vendor of this device and is internally

hardwired to be 8086 hex.

Table 60. Device ID Register

•

Primary byte offset: 03:02h and 43:42h

•

Secondary byte offset: 43:42h and 03:02h

Bit

Name

R/W

Description

15:0

Device ID

R

Device ID identifies this device as the 21555 and is internally hardwired to be

B555h.