Upstream memory 2 window size – Intel 21555 User Manual

Page 38

38

21555 Non-Transparent PCI-to-PCI Bridge User Manual

Address Decoding

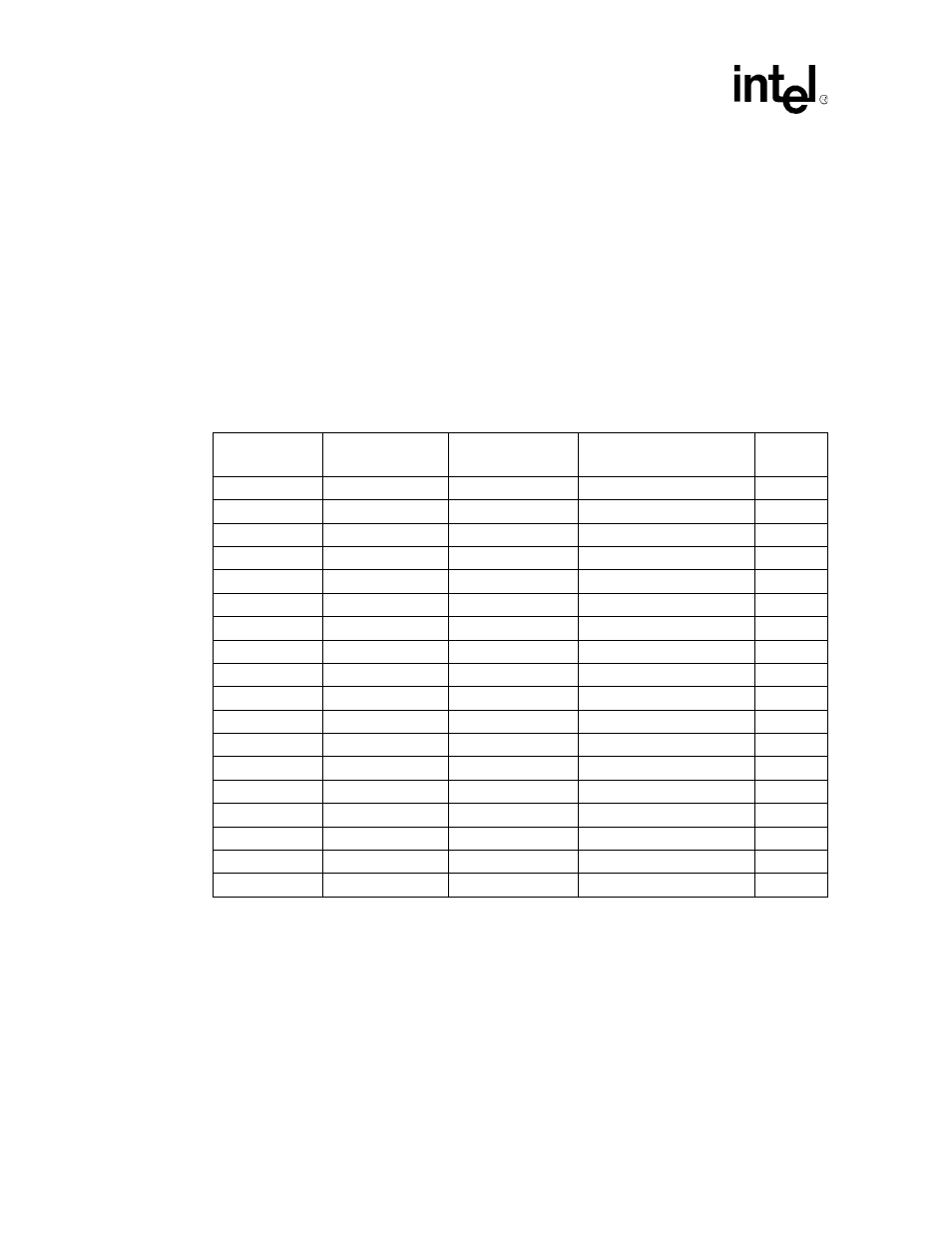

The Upstream Memory 2 address range consists of a fixed number (64) of pages. The page size is

programmable in the Chip Control 1 configuration register. Therefore, the size of the Upstream

Memory 2 BAR is dependent on the page size. The page size varies between 256 bytes to 32 MB

by powers of 2. This results in a window size that varies from 16 KB to 2 GB. This BAR can also

be disabled.

Each page of the upstream window has a corresponding translated base address.

The size of the translated base address varies with the page size and window size. The translated base address

replaces both the original base address and the lookup table index bits. The address bits used for the original base

address for a given page and window size are listed in

, as well as the locations of the six address bits

needed to select one of the 64 entries in the lookup table. The offset of the address, which is not translated, consists

of the remaining lower order address bits.

shows the Upstream Memory 2 window size, with base address,

index, and offset fields.

Table 11. Upstream Memory 2 Window Size

Page Size

(bytes)

Window Size

(bytes)

Base Address

(bits)

Lookup Table Index

(bits)

Offset

(bits)

256

16K

[31:14]

[13:8]

[7:0]

512

32K

[31:15]

[14:9]

[8:0]

1K

64K

[31:16]

[15:10]

[9:0]

2K

128K

[31:17]

[16:11]

[10:0]

4K

256K

[31:18]

[17:12]

[11:0]

8K

512K

[31:19]

[18:13]

[12:0]

16K

1M

[31:20]

[19:14]

[13:0]

32K

2M

[31:21]

[20:15]

[14:0]

64K

4M

[31:22]

[21:16]

[15:0]

128K

8M

[31:23]

[22:17]

[16:0]

256K

16M

[31:24]

[23:18]

[17:0]

512K

32M

[31:25]

[24:19]

[18:0]

1M

64M

[31:26]

[25:20]

[19:0]

2M

128M

[31:27]

[26:21]

[20:0]

4M

256M

[31:28]

[27:22]

[21:0]

8M

512M

[31:29]

[28:23]

[22:0]

16M

1G

[31:30]

[29:24]

[23:0]

32

2G

[31]

[30:25]

[24:0]