14 jtag registers, 126 jtag instruction register options, Jtag – Intel 21555 User Manual

Page 190: Registers

190

21555 Non-Transparent PCI-to-PCI Bridge User Manual

List of Registers

16.14

JTAG

Registers

This chapter presents the theory of operation information about the 21555 JTAG registers. See

for

theory of operation information.

5:4

Reserved

R

Returns 0 when read.

6

REM STAT

R/

W1TC

Signal p_enum_l Removal Status. The 21555 sets this bit to a 1 when

l_stat is sampled high and p_rst_l is deasserted, signaling an

impending removal. This bit is cleared when software writes a 1.

Clearing this bit causes the 21555 to tristate l_stat. Writing a 0 has no

effect.

•

When 1, the 21555 is asserting p_enum_l to indicate that the card

is about to be removed.

•

Reset value is 0

7

INS STAT

R/

W1TC

Signal p_enum_l Insertion Status. The 21555 sets this bit to a 1 when

l_stat is sampled low (ejector handle is closed), the serial preload is

complete and the Primary Lockout Reset Value bit is cleared, indicating

that the card is ready for host initialization. This bit is cleared when

software writes a 1. Writing a 0 has no effect.

•

When 1, the 21555 is asserting p_enum_l to indicate that the card

has just been inserted.

•

Reset value is 0

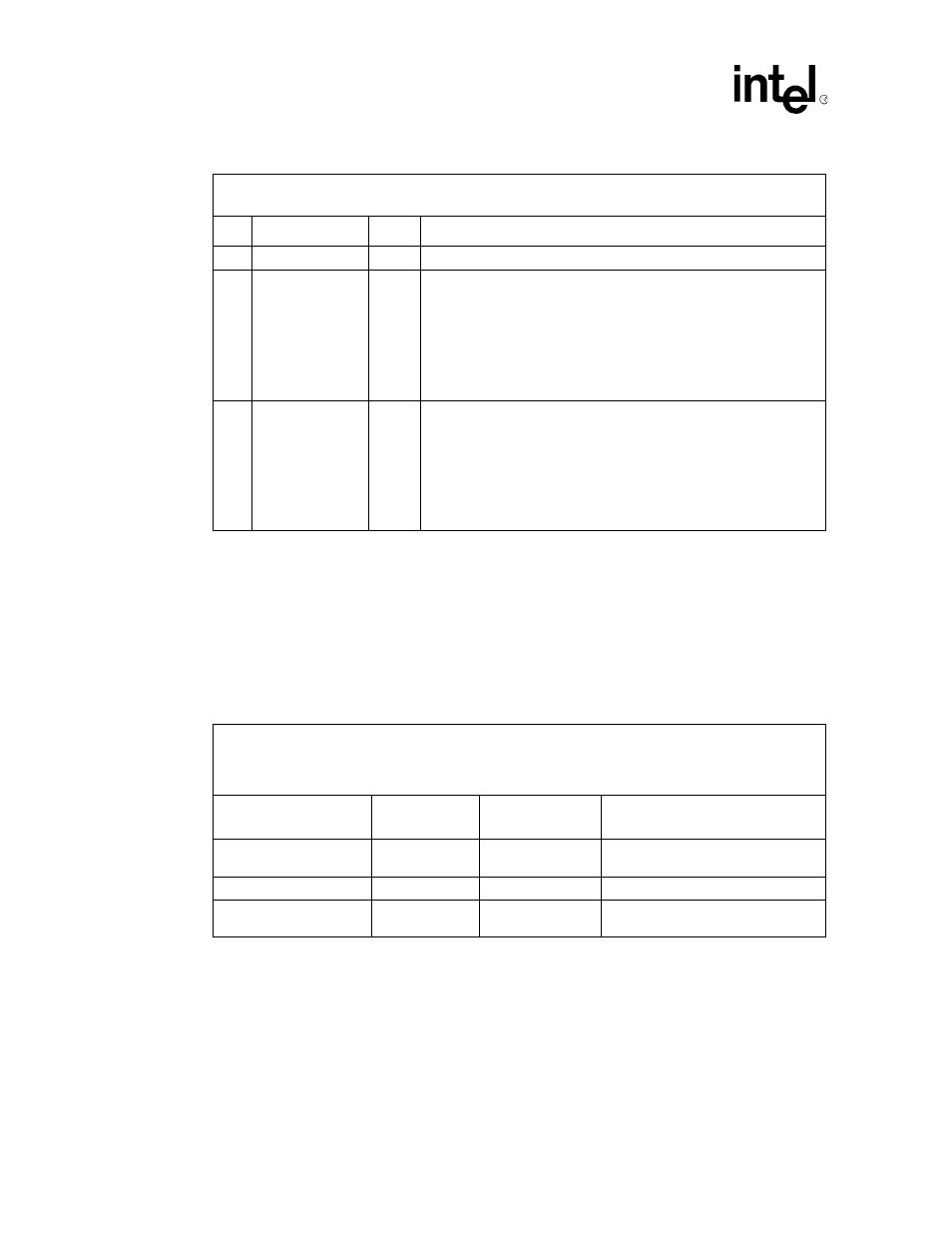

Table 126. JTAG Instruction Register Options (Sheet 1 of 2)

The 4-bit instruction register selects the test mode and features. The instruction codes are shown

in

. These instructions select and control the operation of the boundary-scan and bypass

registers. The instruction register is loaded through the tdi pin. The instruction register has a

serial shift-in stage from which the instruction is then loaded in parallel.

Instruction Register

Contents

Instruction

Name

Test Register

Selected

Operation

0000

EXTEST

Boundary

-

scan

External test (drives pins from

boundary

-

scan register).

0001

SAMPLE

Boundary

-

scan

Samples inputs.

0010

HIGHZ

Bypass

Tristates all output and I/O pins except

the tdo pin.

†

Manufacturer’s identification number: 0000 0001 0011

Design part number: 1001 0010 0110 0010

Version: 0000

Table 125. CompactPCI Hot

-

Swap Control Register (Sheet 2 of 2)

•

Primary byte offset: EF:EEh

•

Secondary byte offset: EF:EEh

Bit

Name

R/W

Description