Table 16-1 – Motorola MC68VZ328 User Manual

Page 297

Programming Model

In-Circuit Emulation

16-5

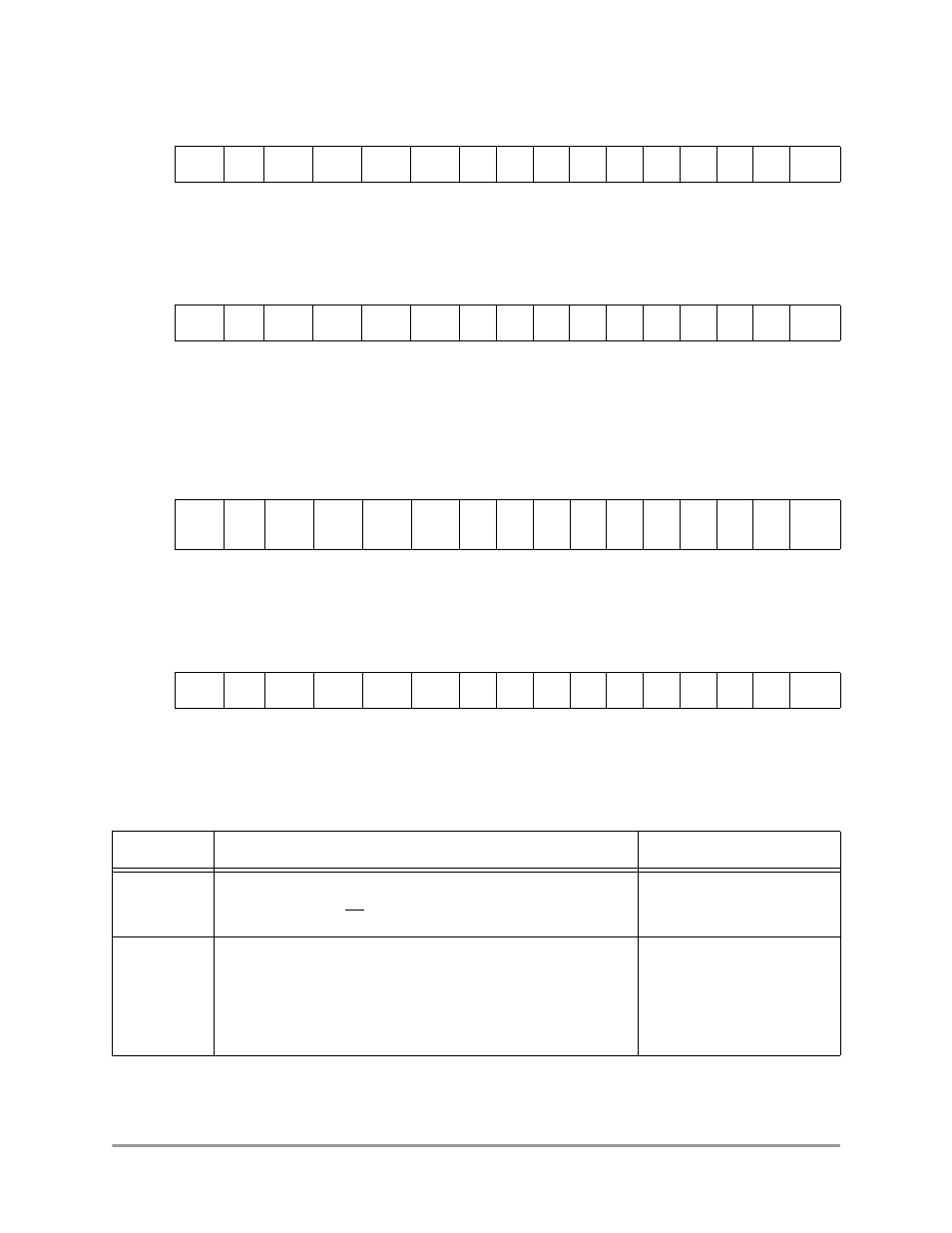

ICEMACR

ICE Module Address Compare Register

0x(FF)FFFFFD00

ICEMAMR

ICE Module Address Mask Register

0x(FF)FFFFFD04

BIT

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

BIT

16

AC3

1

AC

30

AC2

9

AC2

8

AC2

7

AC2

6

AC

25

AC

24

AC

23

AC

22

AC

21

AC

20

AC

19

AC

18

AC

17

AC16

TYPE

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

BIT 0

AC1

5

AC

14

AC1

3

AC1

2

AC1

1

AC1

0

AC

9

AC

8

AC

7

AC

6

AC

5

AC

4

AC

3

AC

2

AC

1

AC0

TYPE

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0

BIT

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

BIT

16

AM3

1

AM

30

AM2

9

AM2

8

AM2

7

AM2

6

A

M2

5

A

M2

4

A

M2

3

A

M2

2

A

M2

1

A

M2

0

A

M1

9

A

M1

8

A

M1

7

AM1

6

TYPE

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0000

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

BIT 0

AM1

5

AM

14

AM1

3

AM1

2

AM1

1

AM1

0

A

M9

A

M8

A

M7

A

M6

A

M5

A

M4

A

M3

A

M2

A

M1

AM0

TYPE

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0000

Table 16-1. ICE Module Address Compare and Mask Registers Description

Name

Description

Setting

ACx

Bits 31–0

Address Compare 31–0—These bits represent the value of the

execution/bus breakpoint address. A match of address bits 31–0

with qualification of AS will generate a match signal.

See description.

AMx

Bits 31–0

Address Mask 31–0—These bits mask the corresponding bits in

the ACx field. With this masking scheme, a break can be made

when the core is accessing a certain range of addresses.

0 = The address is compared

to the current address

cycle.

1 = Forces a true comparison

(“don’t care”) on the

corresponding bit.