4 programming model, 1 pwm 1 control register, Programming model -4 – Motorola MC68VZ328 User Manual

Page 286: Pwm 1 control register -4, Table 15-1, Pwm 1 control register description -4

15-4

MC68VZ328 User’s Manual

Programming Model

15.4

Programming Model

This section contains programming information about both PWM 1 and PWM 2.

15.4.1

PWM 1 Control Register

This register controls the operation of the pulse-width modulator, and it also contains the status of the

PWM 1 FIFO. The register bit assignments are shown in the following register display. The register

settings are described in Table 15-1.

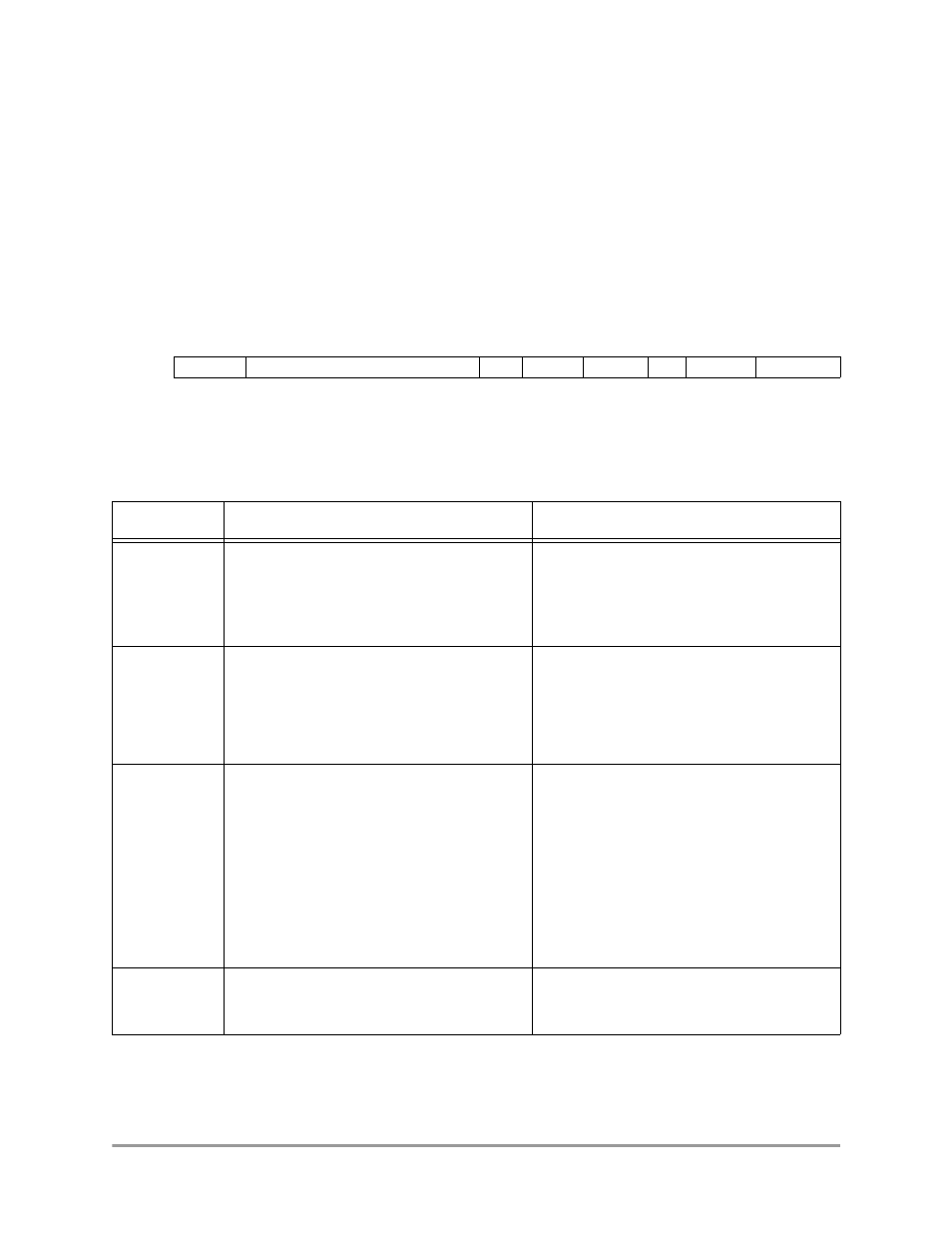

PWMC1

PWM 1 Control Register

0x(FF)FFF500

BIT 15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

BIT 0

CLKSRC

PRESCALER

IRQ

IRQEN

FIFOAV

EN

REPEAT

CLKSEL

TYPE

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

w

w

rw

rw

RESET

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0x0020

Table 15-1. PWM 1 Control Register Description

Name Description

Setting

CLKSRC

Bit 15

Clock Source—This bit is used to select the

clock source to the pulse-width modulator.

0 = SYSCLK source is selected (default).

1 = CLK32 is selected.

Note:

32.768 kHz clock source is selected

when using a 32.768 kHz crystal. If a 38.4 kHz

crystal is used, 38.4 kHz is selected.

PRESCALER

Bits 14–8

Prescaler—This field is used to scale down

the incoming clock to divide by the

prescaler + 1. The prescaler is normally used

to generate a low single-tone PWMO signal.

For voice modulation, these bits are set to 0

(divide by 1). The default value is 0.

Any value between 0 and 127.

IRQ

Bit 7

Interrupt Request—This bit indicates that the

FIFO has one or no bytes remaining, which

can be a signal of the need to fill the FIFO by

writing no more than two 16-bit words into the

PWMS register. This bit automatically clears

itself after this register is read, thus eliminating

an extra write cycle in the interrupt service rou-

tine. If the IRQEN bit is 0, this bit can be polled

to indicate the status of the period comparator.

This bit can be set to immediately post a PWM

interrupt for debugging purposes.

0 = The FIFO is not empty.

1 = The FIFO has one or no sample bytes

remaining.

IRQEN

Bit 6

Interrupt Request Enable—This bit controls

the pulse-width modulator interrupt. While this

bit is low, the interrupt is disabled.

0 = The PWM interrupt is disabled (default).

1 = The PWM interrupt is enabled.