Comtech EF Data MD2401 User Manual

Page 67

MD2401 L-Band Multi Demod Installation and Operation Manual

User Interfaces

MN-MD2401

4–35

Revision 7

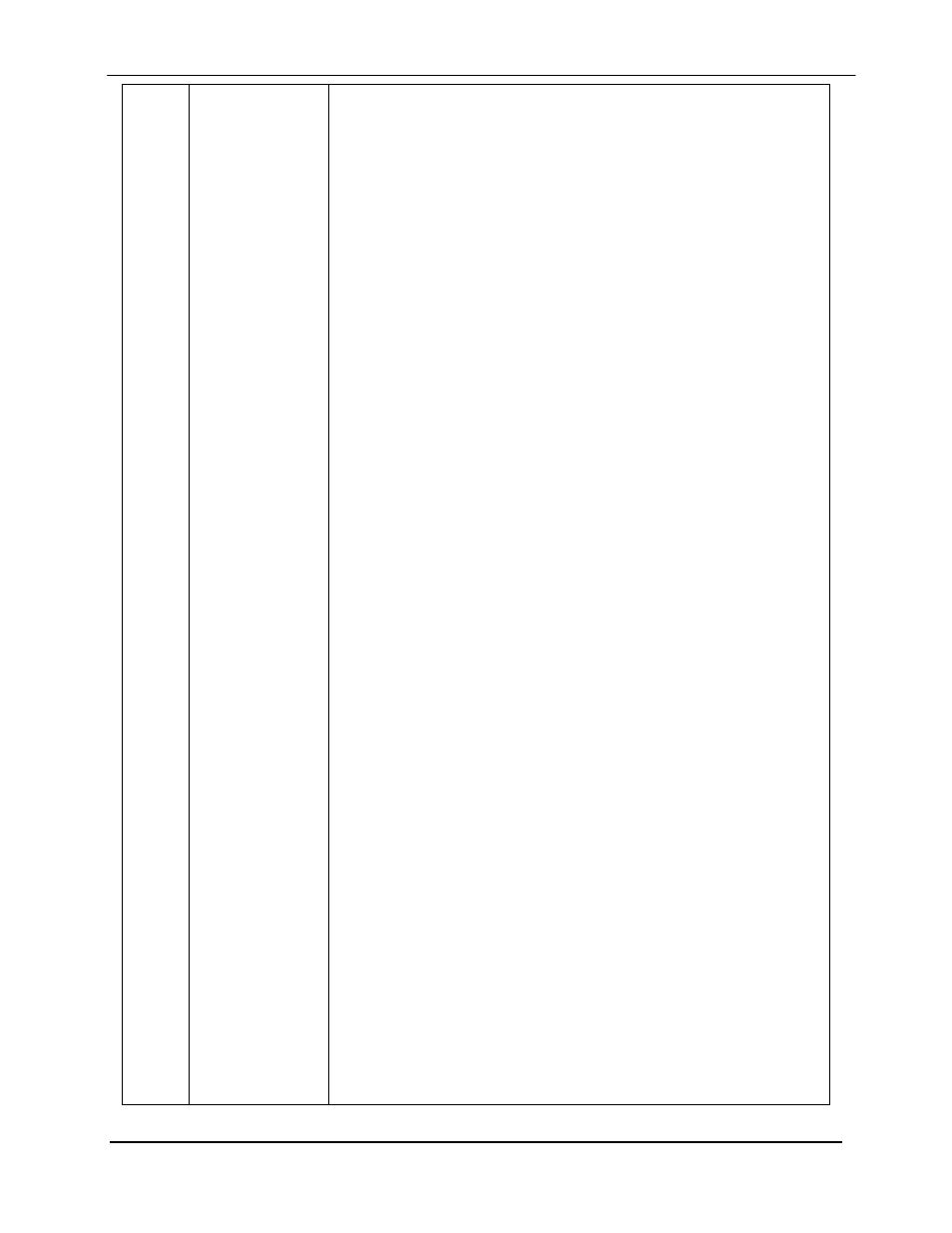

<1>

<4>

<1>

<1>

<1>

<1>

<1>

<1>

<1>

<1>

Spectrum

Buffer Size

Buffer Clock

Buffer Clock

Polarity

Operating Mode

Alarm 1 Mask

Alarm 2 Mask

Alarm 3 Mask

Alarm 4 Mask

Common Alarm 1

Mask

V35_EFRS, 9 = TPC Scrambler

0 = Normal, 1 = Inverted

Byte 1 – 2 = Buffer Size in ms

Byte 3 - 4 = Buffer Size in Bytes

0 = External, 1 = Internal, 2 = EXC, 3 = RX SAT

0 = Normal, 1 = Inverted

0 = Normal, 1 = 2047 Test

Bit 0 = Receive Processor Fault

Bit 1 = Signal Lock Fault

Bit 2 = Receive Satellite AIS Fault

Bit 3 = Rx AGC Level Fault

Bit 4 = Reed-Solomon Sync Fault

Bit 5 = Reed-Solomon Excessive Errors Fault

Bit 6 = Reed-Solomon Uncorrectable Word Fault

Bit 7 = Receive Forced Alarm

(0 = Mask, 1 = Allow)

Bit 0 = Buffer Underflow

Bit 1 = Buffer Overflow

Bit 2 = Buffer Under 10%

Bit 3 = Buffer Over 90%

Bit 4 = Receive FPGA Configuration Fault

Bit 5 = Rx LNB Fault, LBST Only

Bit 6 - 7 = Spares

(0 = Mask, 1 = Allow)

Bit 0 = IF Synthesizer Lock Detect Fault

Bit 1 = Rx Oversample PLL Lock Detect Fault

Bit 2 = Buffer Clock PLL Lock Detect Fault

Bit 3 = Viterbi Decoder Lock Fault

Bit 4 = Sequential Decoder Lock Fault

Bit 5 = Rx 2047 Test Pattern Lock Fault

Bit 6 = External Reference PLL Lock Fault

Bit 7 = Frame Sync Fault

(0 = Mask, 1 = Allow)

Bit 0 = Buffer Clock Activity Detect Fault

Bit 1 = External BNC Activity Detect Fault

Bit 2 = Rx Satellite Clock Activity Detect Fault

Bit 3 = External Reference PLL Activity Fault

Bit 4 = High Stability Activity Detect Fault

Bit 5 = High Stability PLL Fault

Bit 6 = Eb/No Threshold Fault

Bit 7 = Spare

(0 = Mask, 1 = Allow)

Bit 0 = -12 V Alarm

Bit 1 = +12 V Alarm

Bit 2 = +5 V alarm

Bit 3 = Temperature