Comtech EF Data MD2401 User Manual

Page 61

MD2401 L-Band Multi Demod Installation and Operation Manual

User Interfaces

MN-MD2401

4–29

Revision 7

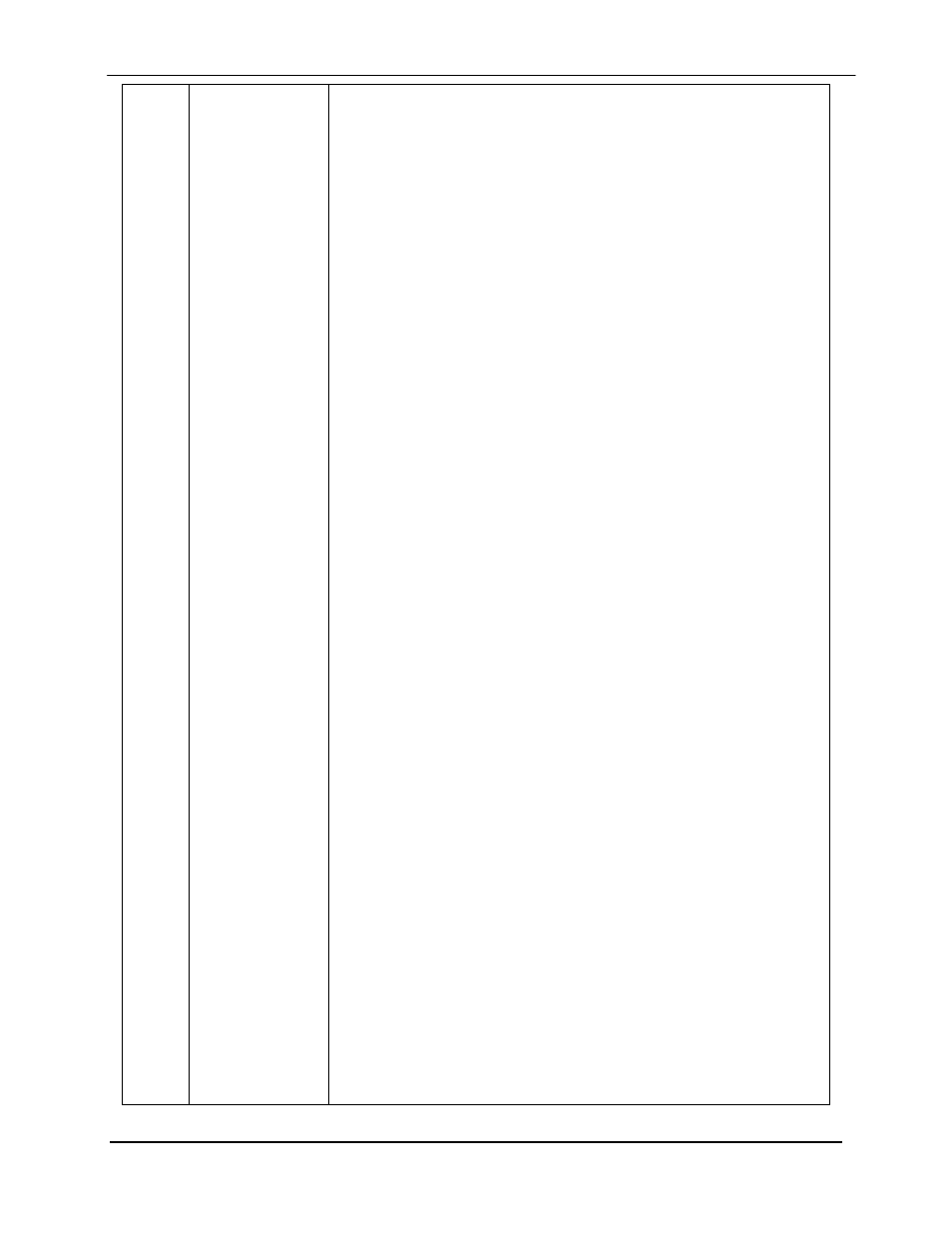

<1>

<1>

<1>

<4>

<4>

<2>

<2>

<2>

<4>

<2>

<1>

<1>

<1>

<1>

Latched Alarm 4

Latched Common

Alarm

Reserved

Error Counter

Test 2047 Error

Counter

Raw BER

Mantissa

Corrected BER

Mantissa

EbNo

Offset Frequency

Test 2047 BER

Mantissa

Raw BER

Exponent

Corrected BER

Exponent

Test 2047 BER

Exponent

Offset Frequency

Sign

Bit 5 = Rx 2047 Test Pattern Lock Fault

Bit 6 = External Reference PLL Lock Fault

Bit 7 = Frame Sync/Multiframe Sync Fault

(0 = Pass, 1 = Fail)

Bit 0 = Buffer Clock Activity Detect Fault

Bit 1 = External BNC Activity Detect Fault

Bit 2 = Rx Satellite Clock Activity Detect Fault

Bit 3 = External Reference PLL Activity Fault

Bit 4 = High Stability Activity Detect Fault

Bit 5 = High Stability PLL Fault

Bit 6 = Eb/No Threshold Fault

Bit 7 = Spare

(0 = Pass, 1 = Fail)

Bit 0 = -12 V Alarm

Bit 1 = +12 V Alarm

Bit 2 = +5 V Alarm

Bit 3 = Temperature Fault

Bit 4 = Interface FPGA Fault

Bit 5 = Battery Fault

Bit 6 = RAM/ROM Fault

Bit 7 = Spare

(0 = Pass, 1 = Fail)

Ignore

Unsigned Binary Value

Unsigned Binary Value

Bytes 1 - 2 = Unsigned Binary Value Raw BER

Bytes 1 - 2 = Unsigned Binary Value Corrected BER

Unsigned Binary Value, 2 Decimal Places Implied

Unsigned Binary Value in Hz, Pos/Neg Indicated Below

Bytes 1 - 2 = Unsigned Binary Value Test 2047 BER

Byte 3 = Unsigned Binary Value Exponent

Byte 3 = Unsigned Binary Value Exponent

Byte 3 = Unsigned Binary Value Exponent

0 = Offset Frequency Pos, 1 = Offset Frequency Neg