Sram memory (u43 & u44) – Altera Stratix II EP2S180 DSP Development Board User Manual

Page 30

2–22

Core Version a.b.c variable

Altera Corporation

Stratix II EP2S180 DSP Development Board Reference Manual

Board Components

SRAM Memory (U43 & U44)

U43 and U44 are two 256 Kbyte x 16-bit asynchronous SRAM devices.

They are connected to the Stratix II device so they can be used by a

Nios

®

II embedded processor as general-purpose memory. The two 16-bit

devices can be used in parallel to implement a 32-bit wide memory

subsystem. Refer to

for Stratix II device pin-outs for SRAM

devices U43 and U44.

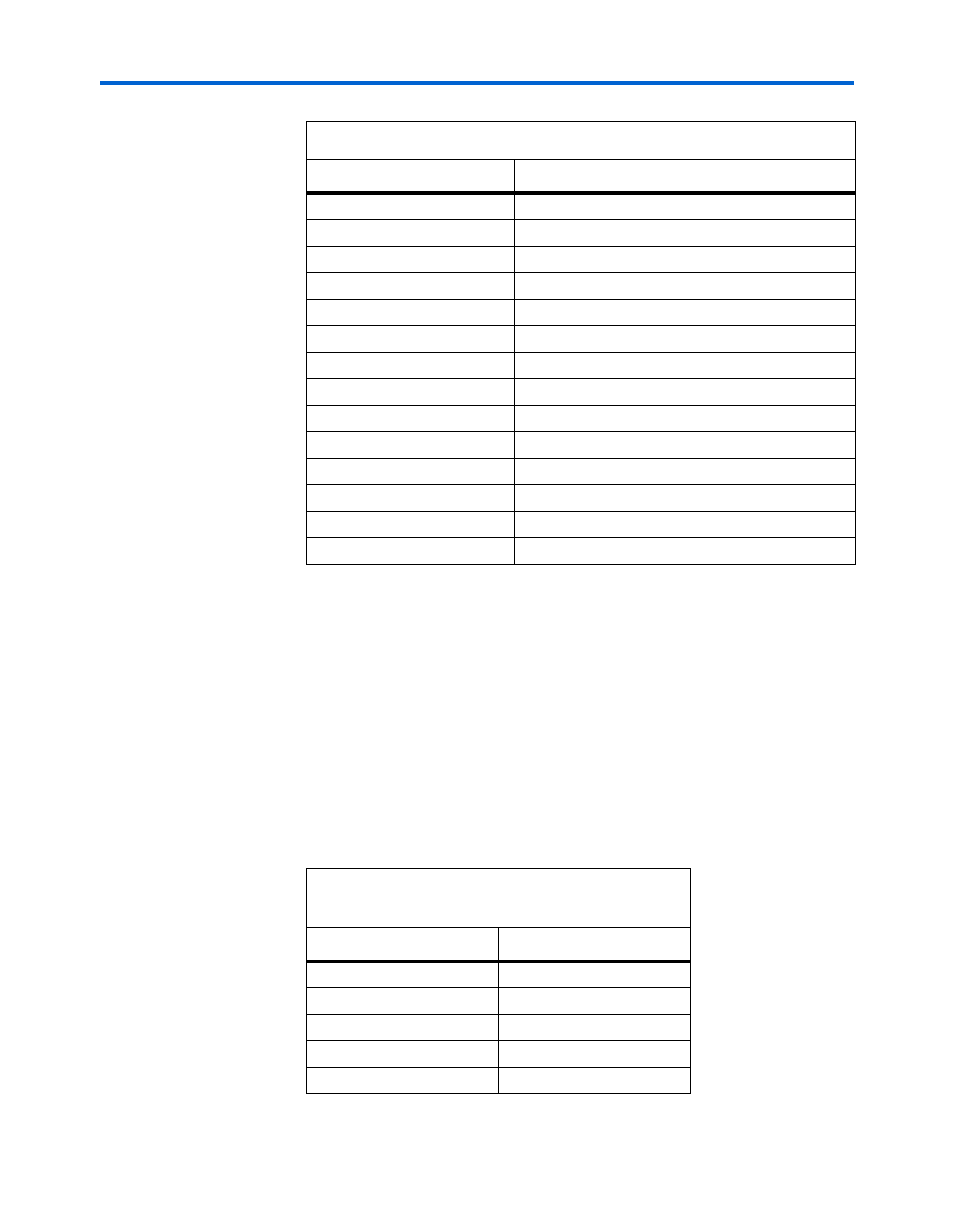

Table 2–18. D/A B (U15, J17) Stratix II Pin-Outs

Signal Name

Stratix II Pin

dacB_D1 (MSB)

W4

dacB_D2

W5

dacB_D3

Y6

dacB_D4

Y7

dacB_D5

Y8

dacB_D6

Y9

dacB_D7

Y10

dacB_D8

Y11

dacB_D9

AB5

dacB_D10

AB6

dacB_D11

AA10

dacB_D12

AA11

dacB_D13

AA6

dacB_D14 (LSB)

AA7

Note to

Table 2–18

:

(1)

The Texas Instruments (TI) naming conventions differ from those of Altera

Corporation. The TI data sheet for the DAC 904 D/A converter lists bit 1 as the

most significant bit (MSB) and bit 14 as the least significant bit (LSB).

Table 2–19. SRAM Memory (U43 & U44) (Part 1

of 3)

Pin Name

Pin Number

SE_A0

AD8

SE_A1

AM27

SE_A2

AM28

SE_A3

AJ27

SE_A4

AK27