Altera Nios Development Board Cyclone II Edition User Manual

Page 55

Altera Corporation

Reference Manual

2–43

May 2007

Nios Development Board Cyclone II Edition

Board Components

The FPGA receives clock input from buffer U2, and from the PROTO1 and

PROTO2 connectors, as shown in

The FPGA can synthesize new clock signals internally using on-chip

PLLs, and drive the clocks to various components on the board, as shown

in

The 50 MHz oscillator (Y2) is socketed and can be changed or removed by

the user. To drive the clock circuitry using the external clock connector

(J4), remove Y2.

1

The factory-programmed configuration controller and Altera-

provided reference designs work only with the 50 MHz clock.

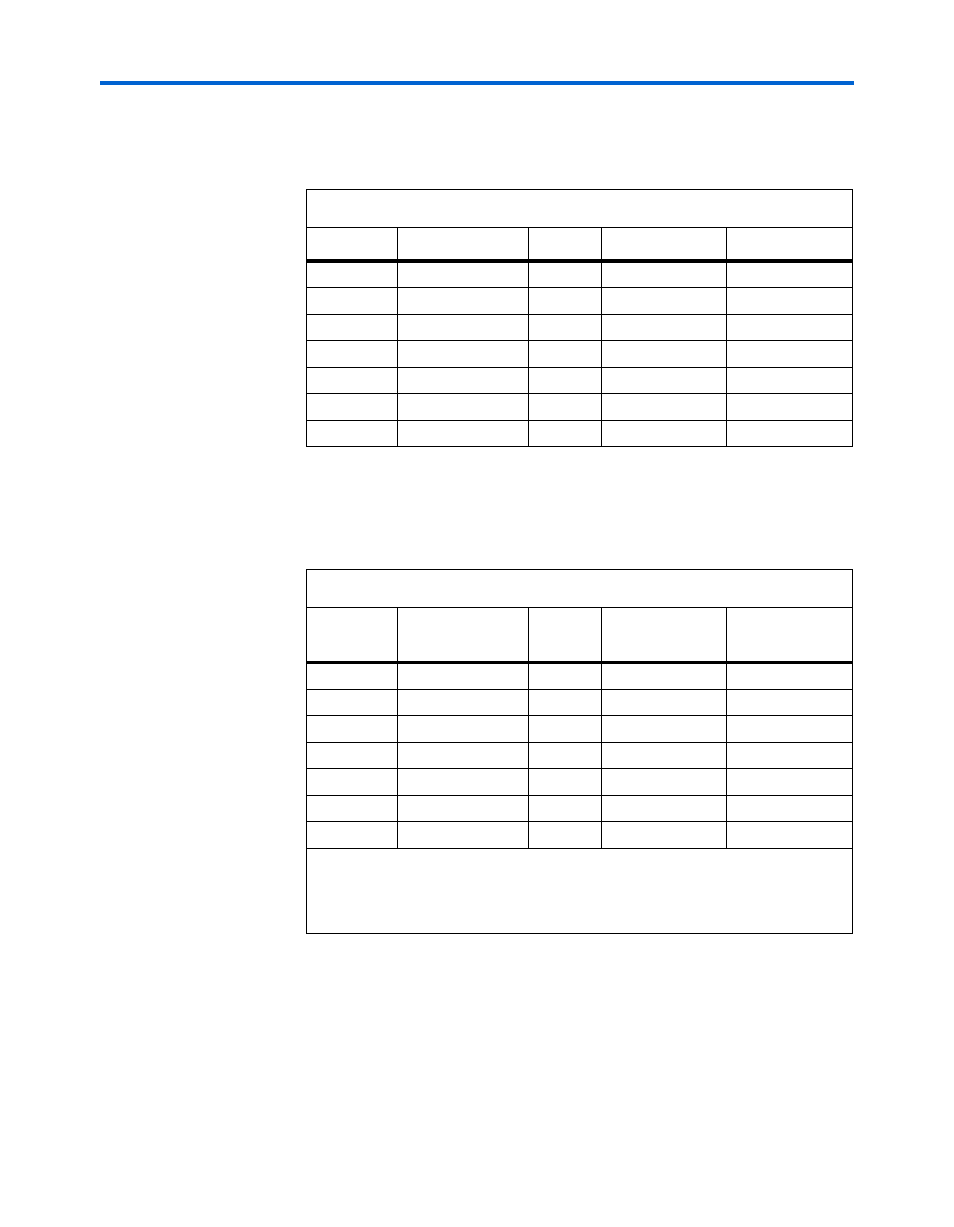

Table 2–21. FPGA Clock Input Pin Table

FPGA Pin

FPGA Pin Name

PLL

Signal Source

Board Net Name

B25

IO

N/A

J25 pin 6

mictor_TRCLK

N26

CLK5

PLL2

J13 pin 13

proto1_CLKOUT

AF4

CLK13

PLL4

J17 pin 13

proto2_CLKOUT

P25

CLK6

PLL2

U2 pin 2

osc_CLK0

AC13

CLK15

PLL4

U2 pin 3

osc_CLK1

N2

CLK0

PLL1

U2 pin 4

sram_CLKIN

B13

CLK8

PLL3

U2 pin 6

sdram_CLKIN

Table 2–22. FPGA Clock Output Pin Table

FPGA Pin

FPGA Pin Name

PLL

(1)

Signal

Destination

Board Net Name

AA7

PLL1_OUTp

PLL1

U63 pin 45

sdram_CLK_p

AA6

PLL1_OUTn

PLL1

U63 pin 46

sdram_CLK_n

E5

PLL3_OUTp

PLL3

U74 pin 89

sram_CLK

W26

IO

N/A

JH1 pin 13

pmc_CLK

F21

PLL2_OUTp

PLL2

J13 pin 11

proto1_PLLCLK

F20

PLL2_OUTn

PLL2

J17 pin 11

proto2_PLLCLK

V21

PLL4_OUTp

PLL4

J25 pin 5

mictor_CLK

Note to

(1)

PLLs are only dedicated when using the Enhanced PLL. If you use the Fast PLL,

the PLL inputs and outputs are interchangeable. For more information on using

PLLs in the Cyclone II refer to the data sheet.